# 1. PCIe-5111B/5112B Specifications

#### **Multi-functional Data Acquisition Boards**

#### Overview

JYTEK JY-5110 series includes PCle-5111B/5112B. PCle-5111B provide up to 32 channels of analog inputs of up to 500K samples per second, 4 channels of analog outputs, 48 channels of digital IO or 4 32-bit counters/timers; PCle-5112B provide up to 16 channels of analog inputs of up to 250K samples per second, 2 channels of analog outputs, 24 channels of digital IO or 2 32-bit counters/timers.

• Please download JYTEK < JYPEDIA>, you can quickly inquire the product prices, the key features and available accessories.

#### 1.1. Main Features

- High accuracy: 260 ppm (JY-5111B/JY-5112B)

- Up to 32 single-ended/16 differential analog input channels(5111B); Up to 16 singleended/8 differential analog input channels(5112B);

- Sampling rates: 500 kS/s for one channel, 300 kS/s for multi-channel(5111B); 250 kS/s for one channel, 250 kS/s for multichannel(5112B).

- 16 bits ADC

- Up to 128M samples of analog input FIFO buffer

- JY-5111B/5112B support 60 V Isolation

- 4(5111B)/2(5112B) simultaneous 16-bit analog output channels

- 32M sample FIFO buffer for analog output

- DMA for AI, AO and DIO

- Analog/Digital/Software Trigger

# 1.2. Analog Input

| Analog Input                                                | 5111B                                      | 5112B          |  |

|-------------------------------------------------------------|--------------------------------------------|----------------|--|

| Number of channels                                          | 32 SE / 16 DIFF                            | 16 SE/ 8 DIFF  |  |

| ADC resolution (Bits)                                       | 16                                         | 6 bits         |  |

| Single channel maximum sample rate                          | 500 kS/s                                   | 250 kS/s       |  |

| Multichannel maximum sample rate with same range(aggregate) | 300 kS/s                                   | 250 kS/s       |  |

| Clock                                                       | 100                                        | O MHz          |  |

| Input range(V)                                              | ±10/±5/±2.5/                               | ±1.25/±0.625   |  |

| Input mode                                                  | RSE / NRSE                                 | / Differential |  |

| Input impedance                                             | >1 GΩ                                      | 2  100 pF      |  |

| Input coupling                                              | D                                          | С              |  |

| Overvoltage protection                                      | ±25 V                                      |                |  |

| CMRR                                                        | 85                                         | dB             |  |

| Crosstalk                                                   | -80                                        | dB             |  |

| DNL                                                         | No Miss                                    | ing Code       |  |

| INL                                                         | 70 ppm of Range Typical                    |                |  |

| Input FIFO                                                  | 128 M Samples                              |                |  |

| Trigger type                                                | Digital, Analog, Software                  |                |  |

| Trigger mode                                                | StartTrigger, ReferenceTrigger, ReTrigger  |                |  |

| Analog trigger voltage range                                | ±10 V Software                             | Programmable   |  |

| Overveltage Protection                                      | Continuous : 8 mA, ±20 V                   |                |  |

| Overvoltage Protection                                      | Instantaneous : 15mA, ±25 V                |                |  |

| Isolation(Channel-to-earth ground)                          | 60 V DC, Measurement Category I,Continuous |                |  |

Table 1 Analog Input Specifications

# 1.3. Analog Output

| Analog Output      |            | 5111B                        | 5112B |  |

|--------------------|------------|------------------------------|-------|--|

| Number of channels |            | 4                            | 2     |  |

| DAC resolution     |            | 16 t                         | oits  |  |

|                    | 1 channel  | 2 M                          | S/s   |  |

| Maximum update     | 2 channels | 2 MS/s (1 channel per bank)* |       |  |

| rate(simultaneous) | 3 channels | 1 M                          | S/s   |  |

|                    | 4 channels | 1 M                          | S/s   |  |

| Clock              |            | 100 MHz                      |       |  |

| Clock accu         | ıracy      | Jitter <20 ps                |       |  |

| Output ran         | ge(V)      | ±10                          |       |  |

| Output mode        |            | RSE                          |       |  |

| Output impedance   |            | 2 Ω                          |       |  |

| Output cou         | ıpling     | DC                           |       |  |

| Output curre       | nt drive   | ±10 mA                       |       |  |

| Output FIFO        |            | 32 M Samples                 |       |  |

| Trigger type       |            | Digital, Software            |       |  |

| Trigger mode       |            | StartTrigger                 |       |  |

<sup>\*</sup>Each bank consists of 2 AO channels. Any channels being used within a single bank will update

Table 2 Analog Output Specifications

# 1.4. Counter Input/Output

| CIO                | 5111B                        | 5112B            |  |

|--------------------|------------------------------|------------------|--|

| Number of channels | 4                            | 2                |  |

| Resolution         | 32 t                         | oits             |  |

| Input Terminal     | Gate(Z) ,Source(A) ,Aux(B) , |                  |  |

|                    | Digital 1                    | rigger           |  |

|                    | External Sai                 | mple Clock       |  |

| Output Terminal    | OU                           | IT               |  |

| Input Mode         | Single,Finite,               | Continuous       |  |

|                    | Edge Counting                |                  |  |

|                    | Period Measure               |                  |  |

|                    | SemiPeriod Measure           |                  |  |

| Input Type         | Frequency Measure            |                  |  |

| input Type         | Pulse Measure                |                  |  |

|                    | Two Edge Separation Measure  |                  |  |

|                    | Quadrature Encoder           |                  |  |

|                    | Two Pulse                    | Encoder          |  |

| Internal timebase  | 100MHz/5M                    | Hz/100kHz        |  |

| Max SampleClock    | 10 N                         | ЛНZ              |  |

| External timebase  | 0-10                         | M Hz             |  |

| Output Mode        | Single, Finite and           | Continuous pulse |  |

| FIFO per channel   | 4 M Samples                  |                  |  |

**Table 3 Counter Input Operations Specifications**

# 1.5. Digital IO Specifications

| DIO                            | 5111B                                                         | 5112B                   |  |

|--------------------------------|---------------------------------------------------------------|-------------------------|--|

| Number of channels             | 48 lines                                                      | 24 lines                |  |

| Number of Dynamic DIO channels | 32 lines<br>(line0~line31)                                    | 24 lines (line0~line23) |  |

| Ground reference               |                                                               | DGND                    |  |

| Directional control            | Independent                                                   | control of each line    |  |

| DI FIFO                        | 16N                                                           | /I Samples              |  |

| DO FIFO                        | 16N                                                           | /I Samples              |  |

| Clock                          | •                                                             | 10 MHz                  |  |

| Initial state                  |                                                               | Input                   |  |

|                                | Logic Low: Max: 1.75 V                                        |                         |  |

| Digital Input                  | Logic High: V <sub>H</sub> Min : 3.5 V                        |                         |  |

|                                | Input Impedance : 50k (Pull Down)                             |                         |  |

|                                | Logic Low :0~1.3 V, I <sub>OL</sub> : 0~32 mA                 |                         |  |

| Digital Output                 | Logic High: 3.5 V~5 V, I <sub>OH</sub> : -32 mA~0mA           |                         |  |

|                                | Output Impedance : 50 Ω                                       |                         |  |

|                                | Continuous 40 mA, -1.8 V~6.8 V                                |                         |  |

| Overvoltage Protection         | Duty cycle of instantaneous current pulse does not exceed 15% |                         |  |

Table 4 Digital IO Specifications

# 1.6. PFI Specifications

| PFI                                | 5111B 5112B                  |  | 5111B 5112B |  |

|------------------------------------|------------------------------|--|-------------|--|

| Number of channels                 | 16                           |  |             |  |

| External digital trigger interface | Trigger voltage : 5V TTL     |  |             |  |

| External digital trigger interface | Trigger edge: Rising/Falling |  |             |  |

| Initial state                      | Input                        |  |             |  |

Table 5 PFI Specifications

# 1.7. Basic DC AI Accuracy

| JY-5111B/J                          | JY-5111B/JY-5112B Basic Accuracy = ±(% Reading+% Range)                          |         |         |          |                                 |                                   |                           |

|-------------------------------------|----------------------------------------------------------------------------------|---------|---------|----------|---------------------------------|-----------------------------------|---------------------------|

| Nominal<br>Range (V)                | 24 Hour To                                                                       | al ±1°C | 90 Days | Tcal±5°C | 24 Hr Full<br>Scale<br>Accuracy | 90 Days<br>Full Scale<br>Accuracy | Full Scale<br>Accuracy(%) |

| 0.625                               | 0.006 +                                                                          | 0.034   | 0.015 + | 0.034    | 250 uV                          | 300 uV                            | 0.048                     |

| 1.25                                | 0.006 +                                                                          | 0.023   | 0.013 + | 0.023    | 350 uV                          | 450 uV                            | 0.036                     |

| 2.5                                 | 0.006 +                                                                          | 0.020   | 0.013 + | 0.020    | 620 uV                          | 810 uV                            | 0.033                     |

| 5                                   | 0.006 +                                                                          | 0.016   | 0.013 + | 0.016    | 1100 uV                         | 1400 uV                           | 0.028                     |

| 10                                  | 0.006 +                                                                          | 0.013   | 0.013 + | 0.013    | 1800 uV                         | 2600 uV                           | 0.026                     |

| Accuracy valid to 95% of full range |                                                                                  |         |         |          |                                 |                                   |                           |

| Note: The 90                        | Note: The 90-day data is estimated based on multiplying the 24-hour data by 2.5. |         |         |          |                                 |                                   |                           |

Table 6 Basic Accuracy in DAQ Mode

# 1.8. AI Bandwidth

| Analog Input Bandwidth       |                      |  |  |

|------------------------------|----------------------|--|--|

| Nominal Range Full Scale (V) | -3dB Bandwidth (KHz) |  |  |

| ±10                          | 325                  |  |  |

| ±5                           | 390                  |  |  |

| ±2.5                         | 480                  |  |  |

| ±1.25                        | 480                  |  |  |

| ±0.625                       | 480                  |  |  |

Table 7 AI Bandwidth Specifications

# 1.9. Basic AO Accuracy

| JY-5111B/JY-5112B AO Basic Accuracy = ±(% Output+% Range) |           |                                                                                  |         |        |      |        |                                 |         |                               |

|-----------------------------------------------------------|-----------|----------------------------------------------------------------------------------|---------|--------|------|--------|---------------------------------|---------|-------------------------------|

| Nominal<br>Range (V)                                      | 24 Hou    | ır Tca                                                                           | al ±1°C | 90 Day | s Tc | al±5°C | 24 Hr Full<br>Scale<br>Accuracy | •       | Full Scale<br>Accuracy(<br>%) |

| 10                                                        | 0.006     | +                                                                                | 0.012   | 0.015  | +    | 0.012  | 1800 uV                         | 2700 uV | 0.027                         |

| Accuracy valid to 95% of full range                       |           |                                                                                  |         |        |      |        |                                 |         |                               |

| Note: The 9                                               | 0-day dat | Note: The 90-day data is estimated based on multiplying the 24-hour data by 2.5. |         |        |      |        |                                 |         |                               |

Table 8 Basic AO Accuracy

# 1.10. System Noise

|          | 5111B              | 5112B              |  |

|----------|--------------------|--------------------|--|

| Range(V) | SystemNoise(µVrms) | SystemNoise(µVrms) |  |

| 0.625    | 7                  | 2                  |  |

| 1.25     | 93                 |                    |  |

| 2.5      | 145                |                    |  |

| 5        | 227                |                    |  |

| 10       | 335                |                    |  |

Table 9 System Noise for PCIe-5111B

# 1.11. Physical and Environment

## **Operating Environment**

| Ambient temperature range | 0 °C to 50 °C             |

|---------------------------|---------------------------|

| Relative humidity range   | 20% to 80%, noncondensing |

## Storage Environment

| Ambient temperature range | -20 °C to 80 °C           |  |

|---------------------------|---------------------------|--|

| Relative humidity range   | 10% to 90%, noncondensing |  |

Table 10 Physical and Environment

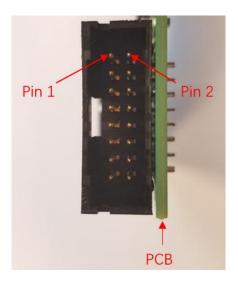

# 1.12. Front Panel and Pin Definition

Figure 1 PCIe 5111B Front Panel

|     | Connector 0            |     |                       |  |  |  |

|-----|------------------------|-----|-----------------------|--|--|--|

| Pin | Identification         | Pin | Identification        |  |  |  |

| 1   | PFI 14 /DO ECLK/ DIO46 | 35  | D GND                 |  |  |  |

| 2   | PFI 12/ DIO44          | 36  | D GND                 |  |  |  |

| 3   | PFI 9/ DIO41           | 37  | PFI 8/ DIO40          |  |  |  |

| 4   | D_GND                  | 38  | PFI 7/ DIO39          |  |  |  |

| 5   | PFI 6/ AO_ECLK/ DIO38  | 39  | PFI 15/ DIO47         |  |  |  |

| 6   | PFI 5/ DIO37           | 40  | PFI 13/ DIO45         |  |  |  |

| 7   | D_GND                  | 41  | PFI 4/ DIO36          |  |  |  |

| 8   | +5V_OUT                | 42  | PFI 3/ DIO35          |  |  |  |

| 9   | D_GND                  | 43  | PFI 2 /AI_ECLK/ DIO34 |  |  |  |

| 10  | PFI 1/ DIO33           | 44  | DGND                  |  |  |  |

| 11  | PFI 0/ DIO32           | 45  | PFI 10/DI_ECLK/ DIO42 |  |  |  |

| 12  | D_GND                  | 46  | PFI 11/ DIO43         |  |  |  |

| 13  | D_GND                  | 47  | DIO 3                 |  |  |  |

| 14  | +5V_OUT                | 48  | DIO 7                 |  |  |  |

| 15  | D_GND                  | 49  | DIO 2                 |  |  |  |

| 16  | DIO 6                  | 50  | D_GND                 |  |  |  |

| 17  | DIO 1                  | 51  | DIO 5                 |  |  |  |

| 18  | D_GND                  | 52  | DIO 0                 |  |  |  |

| 19  | DIO 4                  | 53  | D_GND                 |  |  |  |

| 20  | RSVD                   | 54  | AO_COM                |  |  |  |

| 21  | AO 1                   | 55  | AO_COM                |  |  |  |

| 22  | AO 0                   | 56  | AI_COM                |  |  |  |

| 23  | Al 15 (Al 7-)          | 57  | Al 7 (Al 7+)          |  |  |  |

| 24  | AI_COM                 | 58  | AI 14 (AI 6-)         |  |  |  |

| 25  | AI 6 (AI 6+)           | 59  | AI_COM                |  |  |  |

| 26  | Al 13 (Al 5-)          | 60  | AI 5 (AI 5+)          |  |  |  |

| 27  | AI_COM                 | 61  | AI 12 (AI 4-)         |  |  |  |

| 28  | Al 4 (Al 4+)           | 62  | AI_SENSE 0            |  |  |  |

| 29  | AI_COM                 | 63  | Al 11 (Al 3-)         |  |  |  |

| 30  | Al 3 (Al 3+)           | 64  | AI_COM                |  |  |  |

| 31  | AI10 (AI 2-)           |     | Al 2 (Al 2+)          |  |  |  |

| 32  | AI_COM                 | 66  | Al 9 (Al 1-)          |  |  |  |

| 33  | Al 1 (Al 1+)           | _   | AI_COM                |  |  |  |

| 34  | AI 8 (AI 0-)           | 68  | AI 0 (AI 0+)          |  |  |  |

|     | Connector 1    |     |                |  |  |  |  |

|-----|----------------|-----|----------------|--|--|--|--|

| Pin | Identification | Pin | Identification |  |  |  |  |

| 1   | DIO 30         | 35  | D GND          |  |  |  |  |

| 2   | DIO 28         | 36  | D_GND          |  |  |  |  |

| 3   | DIO 25         | 37  | DIO 24         |  |  |  |  |

| 4   | D_GND          | 38  | DIO 23         |  |  |  |  |

| 5   | DIO 22         | 39  | DIO 31         |  |  |  |  |

| 6   | DIO 21         | 40  | DIO 29         |  |  |  |  |

| 7   | D_GND          | 41  | DIO 20         |  |  |  |  |

| 8   | +5V_OUT        | 42  | DIO 19         |  |  |  |  |

| 9   | D_GND          | 43  | DIO 18         |  |  |  |  |

| 10  | DIO 17         | 44  | DGND           |  |  |  |  |

| 11  | DIO 16         | 45  | DIO 26         |  |  |  |  |

| 12  | D_GND          | 46  | DIO 27         |  |  |  |  |

| 13  | D_GND          | 47  | DIO 11         |  |  |  |  |

| 14  | +5V_OUT        | 48  | DIO 15         |  |  |  |  |

| 15  | D_GND          | 49  | DIO 10         |  |  |  |  |

| 16  | DIO 14         | 50  | D_GND          |  |  |  |  |

| 17  | DIO 9          | 51  | DIO 13         |  |  |  |  |

| 18  | D_GND          | 52  | DIO 8          |  |  |  |  |

| 19  | DIO 12         | 53  | D_GND          |  |  |  |  |

| 20  | RSVD           | 54  | AO_COM         |  |  |  |  |

| 21  | AO 3           | 55  | AO_COM         |  |  |  |  |

| 22  | AO 2           | 56  | AI_COM         |  |  |  |  |

| 23  | Al 31 (Al 23-) | 57  | Al 23 (Al 23+) |  |  |  |  |

| 24  | AI_COM         | 58  | Al 30 (Al 22-) |  |  |  |  |

| 25  | Al 22 (Al 22+) | 59  | AI_COM         |  |  |  |  |

| 26  | Al 29 (Al 21-) | 60  | Al 21 (Al 21+) |  |  |  |  |

| 27  | AI_COM         | 61  | Al 28 (Al 20-) |  |  |  |  |

| 28  | AI 20 (AI 20+) | 62  | AI_SENSE 1     |  |  |  |  |

| 29  | AI_COM         | 63  | Al 27 (Al 19-) |  |  |  |  |

| 30  | Al 19 (Al 19+) | 64  | AI_COM         |  |  |  |  |

| 31  | Al26 (Al 18-)  | 65  | AI 18 (AI 18+) |  |  |  |  |

| 32  | AI_COM         | 66  | Al 25 (Al 17-) |  |  |  |  |

| 33  | Al 17 (Al 17+) | 67  | AI_COM         |  |  |  |  |

| 34  | Al 24 (Al 16-) | 68  | Al 16 (Al 16+) |  |  |  |  |

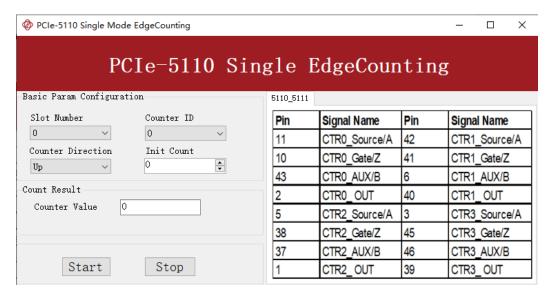

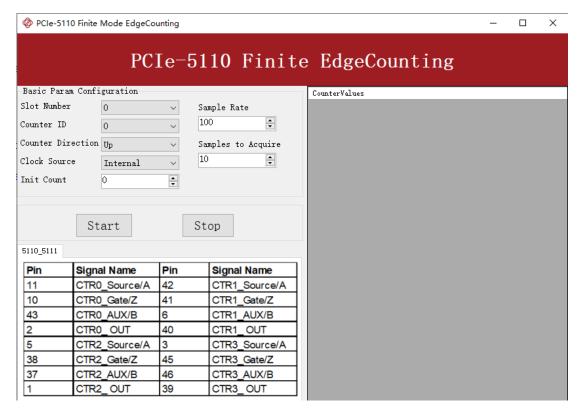

| Pin | Signal Name                | Pin Signal Name  |               |  |  |  |

|-----|----------------------------|------------------|---------------|--|--|--|

| 11  | CTR0_Source/A              | 42               | CTR1_Source/A |  |  |  |

| 10  | CTR0_Gate/Z 41 CTR1_Gate/Z |                  |               |  |  |  |

| 43  | CTR0_AUX/B                 | //B 6 CTR1_AUX/B |               |  |  |  |

| 2   | CTR0_OUT                   | 40               | CTR1_OUT      |  |  |  |

| 5   | CTR2_Source/A              | 3                | CTR3_Source/A |  |  |  |

| 38  | CTR2_Gate/Z                | 45               | CTR3_Gate/Z   |  |  |  |

| 37  | CTR2_AUX/B                 | 46               | CTR3_AUX/B    |  |  |  |

| 1   | CTR2_OUT                   | 39               | CTR3_OUT      |  |  |  |

Table 11 5111B Pin Definition

|     | Conne                   | ector 0 | <del></del>            |

|-----|-------------------------|---------|------------------------|

| Pin | Identification          | Pin     | Identification         |

| 1   | PFI 14 /DO_ECLK/ DIO 22 | 35      | D_GND                  |

| 2   | PFI 12/ DIO 20          | 36      | D_GND                  |

| 3   | PFI 9/ DIO 17           | 37      | PFI 8/ DIO 16          |

| 4   | D_GND                   | 38      | PFI 7/ DIO 15          |

| 5   | PFI 6/ AO_ECLK/ DIO 14  | 39      | PFI 15/ DIO 23         |

| 6   | PFI 5/ DIO 13           | 40      | PFI 13/ DIO 21         |

| 7   | D_GND                   | 41      | PFI 4/ DIO 12          |

| 8   | +5V_OUT                 | 42      | PFI 3/ DIO 11          |

| 9   | D_GND                   | 43      | PFI 2/AI_ECLK/ DIO 10  |

| 10  | PFI 1/ DIO 9            | 44      | DGND                   |

| 11  | PFI 0/ DIO 8            | 45      | PFI 10/DI_ECLK/ DIO 18 |

| 12  | D_GND                   | 46      | PFI 11/ DIO 19         |

| 13  | D_GND                   | 47      | DIO 3                  |

| 14  | +5V_OUT                 | 48      | DIO 7                  |

| 15  | D_GND                   | 49      | DIO 2                  |

| 16  | DIO 6                   | 50      | D_GND                  |

| 17  | DIO 1                   | 51      | DIO 5                  |

| 18  | D_GND                   | 52      | DIO O                  |

| 19  | DIO 4                   | 53      | D_GND                  |

| 20  | RSVD                    | 54      | AO_COM                 |

| 21  | AO 1                    | 55      | AO_COM                 |

| 22  | AO O                    | 56      | AI_COM                 |

| 23  | AI 15 (AI 7-)           | 57      | AI 7 (AI 7+)           |

| 24  | AI COM                  | 58      | AI 14 (AI 6-)          |

| 25  | AI 6 (AI 6+)            | 59      | AI_COM                 |

| 26  | AI 13 (AI 5-)           | 60      | AI 5 (AI 5+)           |

| 27  | AI_COM                  | 61      | AI 12 (AI 4-)          |

| 28  | AI 4 (AI 4+)            | 62      | AI_SENSE O             |

| 29  | AI_COM                  | 63      | AI 11 (AI 3-)          |

| 30  | AI 3 (AI 3+)            | 64      | AI_COM                 |

| 31  | AI10 (AI 2-)            | 65      | AI 2 (AI 2+)           |

| 32  | AI_COM                  | 66      | AI 9 (AI 1-)           |

| 33  | AI 1 (AI 1+)            | 67      | AI_COM                 |

| 34  | AI 8 (AI 0-)            | 68      | AI 0 (AI 0+)           |

| Pin | Signal Name Pin Signal Name |    |               |  |  |  |  |

|-----|-----------------------------|----|---------------|--|--|--|--|

| 11  | CTR0_Source/A               | 42 | CTR1_Source/A |  |  |  |  |

| 10  | CTR0_Gate/Z                 | 41 | CTR1_Gate/Z   |  |  |  |  |

| 43  | CTR0_AUX/B                  | 6  | CTR1_AUX/B    |  |  |  |  |

| 2   | CTR0_OUT                    | 40 | CTR1_ OUT     |  |  |  |  |

Table 12 5112B Pin Definition

# **Table of Contents**

| 1 | . PCle-5111B/5112B Specifications         | 1    |

|---|-------------------------------------------|------|

|   | 1.1. Main Features                        |      |

|   | 1.2. Analog Input                         | 2    |

|   | 1.3. Analog Output                        | 3    |

|   | 1.4. Counter Input/Output                 | 3    |

|   | 1.5. Digital IO Specifications            | 4    |

|   | 1.6. PFI Specifications                   | 4    |

|   | 1.7. Basic DC AI Accuracy                 | 5    |

|   | 1.8. AI Bandwidth                         | 6    |

|   | 1.9. Basic AO Accuracy                    | 6    |

|   | 1.10. System Noise                        | 6    |

|   | 1.11. Physical and Environment            | 6    |

|   | 1.12. Front Panel and Pin Definition      | 7    |

| 2 | . Software                                | . 16 |

|   | 2.1. Supported Operating System           | . 16 |

|   | 2.2. Programming Languages                | . 16 |

| 3 | . Order Information                       | . 16 |

| 4 | . JYPEDIA                                 | . 16 |

| 5 | . Additional Hardware Information         | . 16 |

|   | 5.1. Basic DC AI Accuracy                 | . 17 |

|   | 5.2. Basic AO Accuracy                    | . 17 |

| 6 | . Additional Software Information         | . 19 |

|   | 6.1. System Requirements                  | . 19 |

|   | 6.2. System Software                      | . 19 |

|   | 6.3. C# Programming Language              | . 20 |

|   | 6.4. PCIe-5111B Series Hardware Driver    | . 20 |

|   | 6.5. Install the SeeSharpTools from JYTEK | . 20 |

|   | 6.6. Running C# Programs in Linux         | . 21 |

| 7 | . Operating JY5111B                       | . 22 |

|   | 7.1. Quick Start                          | . 22 |

| 7.2. Data Acquisition Methods        | 22 |

|--------------------------------------|----|

| 7.2.1. Continuous Acquisition        | 26 |

| 7.2.2. Finite Acquisition            | 26 |

| 7.2.3. Single Point Acquisition      | 27 |

| 7.2.4. Record Acquisition            | 27 |

| 7.3. Analog Input Terminal Type      | 27 |

| 7.3.1. DIFF Mode                     | 27 |

| 7.3.2. RSE Mode                      | 29 |

| 7.3.3. NRSE Mode                     | 30 |

| 7.4. Trigger Source                  | 31 |

| 7.4.1. Immediate trigger             | 31 |

| 7.4.2. Software Trigger              | 32 |

| 7.4.3. External Analog Trigger       | 33 |

| 7.4.4. External Digital Trigger      | 39 |

| 7.5. Trigger Mode                    | 41 |

| 7.5.1. Start Trigger                 | 41 |

| 7.5.2. Reference Trigger             | 42 |

| 7.5.3. ReTrigger                     | 43 |

| Learn by Example 7.5                 | 43 |

| 7.6. AO Operations                   | 46 |

| 7.6.1. Finite Output                 | 46 |

| 7.6.2. Continuous NoWrappping Output | 49 |

| 7.6.3. Continuous Wrapping Output    | 52 |

| 7.7. Digital I/O Operations          | 55 |

| 7.7.1. Static DI/DO                  | 55 |

| 7.7.2. Dynamic DI/DO                 | 57 |

| 7.8. Counter Input Operations        | 59 |

| 7.8.1. Edge Counting                 | 60 |

| 7.8.2. Pulse Measurement             | 65 |

| 7.8.3. Frequency Measurement         | 70 |

| 7.8.4. Period Measurement            | 74 |

| 7.8.5. Two-Edge Separation           | 75 |

| 7.8.6. Quadrature Encoder                                     | 79  |

|---------------------------------------------------------------|-----|

| 7.8.7. Two-Pulse Encoder                                      | 84  |

| 7.9. Counter Output Operations                                | 89  |

| 7.9.1. Single Pulse Output                                    | 89  |

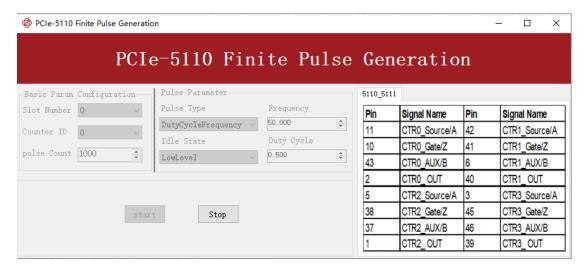

| 7.9.2. Finite Pulse Output                                    | 91  |

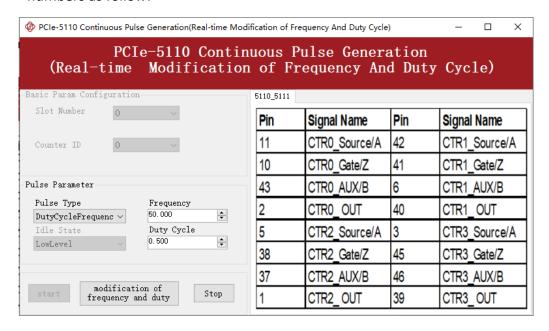

| 7.9.3. Continuous Pulse Output                                |     |

| 7.10. System Synchronization Interface (SSI) for PCIe Modules | 95  |

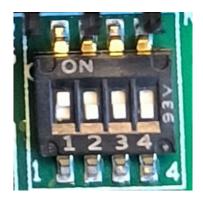

| 7.11. DIP Switch in PCIe-5111B                                | 96  |

| 8. Calibration                                                | 97  |

| 9. Appendix(Measurement Issues)                               |     |

| 9.1. Floating Signals and Ground Referenced Signals           |     |

| 9.2. Differential, NRSE, RSE Modes                            |     |

|                                                               |     |

| 9.3. Reducing the Common Mode Voltage Effect                  |     |

| 9.4. JY-5111B Analog Input Wiring Guide                       |     |

| 10. About JYTEK                                               | 103 |

| 10.1. JYTEK China                                             | 103 |

| 10.2. JYTEK Software Platform                                 | 103 |

| 10.3. JYTEK Warranty and Support Services                     | 103 |

| 11. Statement                                                 | 104 |

|                                                               |     |

| Table 1 Analog Input Specifications                           | 2   |

| Table 2 Analog Output Specifications                          | 3   |

| Table 3 Counter Input Operations Specifications               | 3   |

| Table 4 Digital IO Specifications                             | 4   |

| Table 5 PFI Specifications                                    | 4   |

| Table 6 Basic Accuracy in DAQ Mode                            | 5   |

| Table 7 AI Bandwidth Specifications                           | 6   |

| Table 8 Basic AO Accuracy                                     |     |

| Table 9 System Noise for PCIe-5111B                           | 6   |

| Table 10 Physical and Environment                             |     |

| Table 11 5111B Pin Definition                                 |     |

| Table 12 5112B Pin Definition                                 | 9   |

| Figure 1 PCle 5111B Front Panel                               | 7   |

| Figure 2 Sample Rate and Internal AD Conversion               |     |

| Figure 3 PCIe-5111B experiment                                |     |

|                                                               |     |

| Figure 4 TB-68 Terminal Block                      | 25 |

|----------------------------------------------------|----|

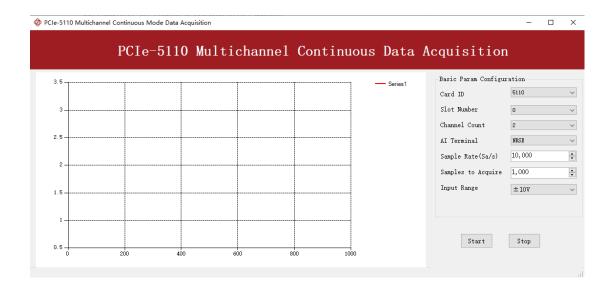

| Figure 5 Continuous MultiChannel Paraments         | 25 |

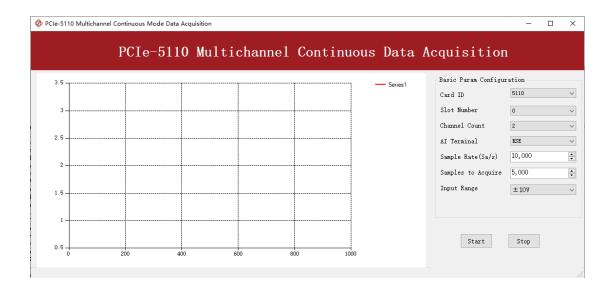

| Figure 6 MultiChannel Continuous Acquisition       | 26 |

| Figure 7 Differential Mode for Grounding Signals   | 28 |

| Figure 8 Choose Differential in AI Terminal        | 29 |

| Figure 9 RSE Mode for Floating Signals             | 30 |

| Figure 10 NRSE Mode for Grounding Signals          | 30 |

| Figure 11 Choose NRSE In Al Terminal               | 31 |

| Figure 12 Immediate trigger Paraments              | 32 |

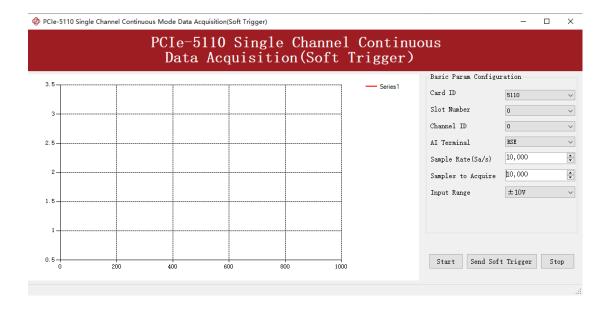

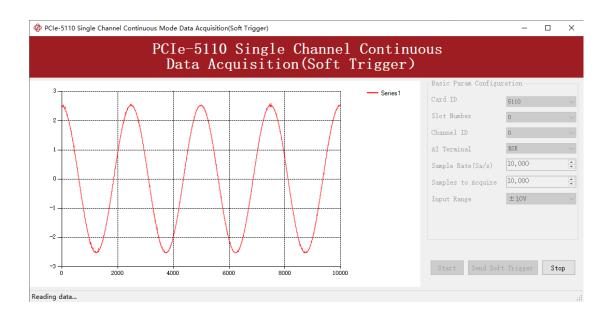

| Figure 13 Software trigger Paraments               | 33 |

| Figure 14 Software trigger Acquisition             | 33 |

| Figure 15 Rising Slope Trigger                     | 34 |

| Figure 16 Falling Slope Trigger                    | 35 |

| Figure 17 Hysteresis with Rising Slope Trigger     | 36 |

| Figure 18 Hysteresis with Falling Slope Trigger    | 36 |

| Figure 19 Entering Window Trigger                  | 37 |

| Figure 20 Leaving Window Trigger                   | 37 |

| Figure 21 Analog Trigger Paraments                 | 38 |

| Figure 22 Waiting For Trigger                      | 38 |

| Figure 23 Analog Trigger Acquisition               | 39 |

| Figure 24 External Digital Trigger                 | 40 |

| Figure 25 Digital Trigger Paraments                | 40 |

| Figure 26 Digital Trigger Acquisition              | 41 |

| Figure 27 Start Trigger                            | 42 |

| Figure 28 Reference Trigger                        | 43 |

| Figure 29 ReTrigger                                | 43 |

| Figure 30 Retrigger Paraments                      | 44 |

| Figure 31 Retrigger In Start Trigger Mode          | 45 |

| Figure 32 Retrigger In Reference Trigger Mode      | 45 |

| Figure 33 Complete Retrigger Count                 | 46 |

| Figure 34 AI Continuous Paraments                  | 47 |

| Figure 35 AO Finite Output Paraments               | 47 |

| Figure 36 AO Finite Signal                         | 48 |

| Figure 37 Al Acquisition Signal                    | 48 |

| Figure 38 AI Continuous Paraments                  | 49 |

| Figure 39 AO ContinuousNoWrapping Output Paraments | 50 |

| Figure 40 AO ContinuousNoWrapping Signal           | 51 |

| Figure 41 Al Acquisition AO Sin Signal             | 51 |

| Figure 42 Update AO Square Signal                  | 52 |

| Figure 43 Al Acquisition AO Square Signal          | 52 |

| Figure 44 Al Continuous Paraments                  |    |

| Figure 45 AO Continuous Wrapping Paraments         | 54 |

| Figure 46 AO Continuous Wrapping Signal            | 54 |

| Figure 47 Al Acquisition AO Signal                 | 55 |

| Figure 48 Single Digit | al Output                               | 56 |

|------------------------|-----------------------------------------|----|

| Figure 49 Single Digit | al Input                                | 57 |

| Figure 50 DI Continuo  | ous Paraments                           | 58 |

| Figure 51 DO Continu   | ousNoWrapping Output                    | 58 |

| Figure 52 DI Continuo  | ous Acquisition                         | 59 |

| Figure 53 Counter Ter  | rminal                                  | 59 |

| Figure 54 Counter Sig  | gnal Wiring Instruction                 | 60 |

| Figure 55 Simple Edg   | e Counting in Single Mode               | 61 |

| Figure 56 Buffered Ed  | dge Counting with Internal Sample Clock | 61 |

| Figure 57 Simple Edg   | e Counting with Implicit SampleClk      | 62 |

| Figure 58 Count Direct | ction                                   | 62 |

| Figure 59 EdgeCount    | ing For Single Mode                     | 63 |

| Figure 60 EdgeCount    | ing For Finite Mode                     | 64 |

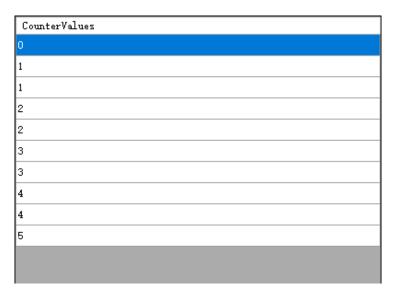

| Figure 61 Counter Val  | lues For Internal Clock                 | 64 |

| Figure 62 Counter Val  | lues For Implicit Clock                 | 65 |

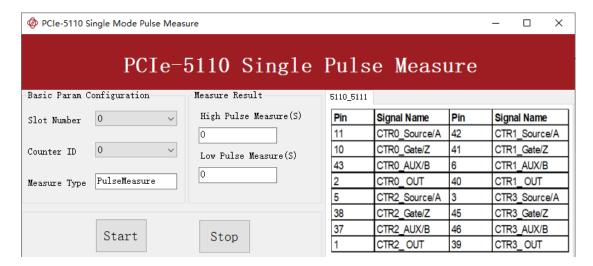

| Figure 63 Pulse Meas   | surement in Single Mode                 | 66 |

| Figure 64 Pulse Meas   | surement with Internal SampleClk        | 66 |

| Figure 65 Pulse Meas   | surement with Implicit SampleClk        | 67 |

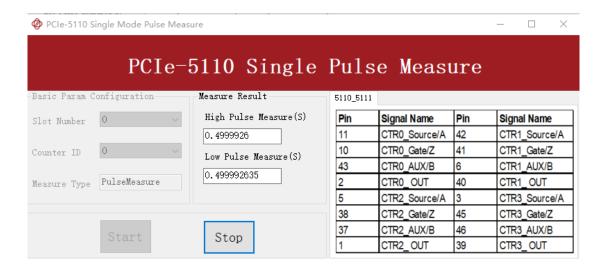

| Figure 66 Pulse Meas   | sure For Single Mode                    | 67 |

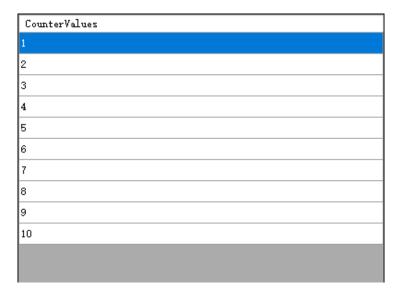

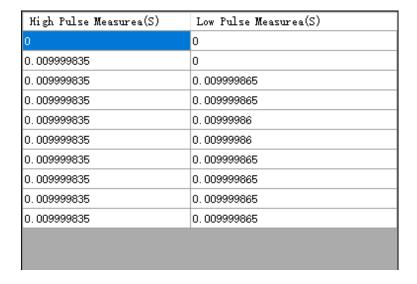

| Figure 67 Pulse Meas   | sure Value For Single Mode              | 68 |

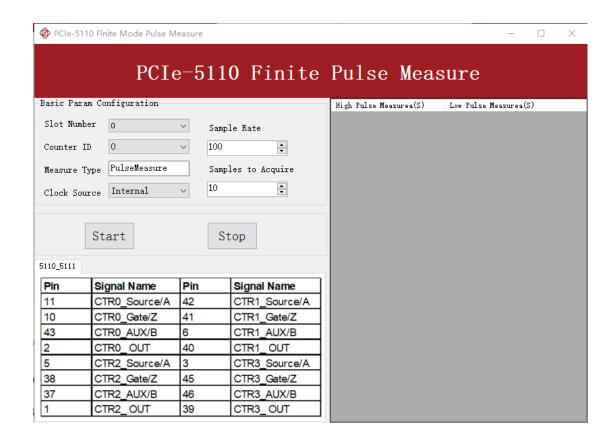

| Figure 68 Pulse Meas   | sure For Finite Mode                    | 69 |

| Figure 69 Pulse Meas   | sure Values For Finite Mode             | 69 |

| Figure 70 Frequency    | Measurement with Internal Sample Clock  | 71 |

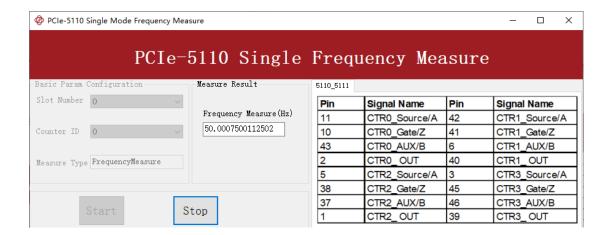

| Figure 71 Frequency    | Measure For Single Mode                 | 72 |

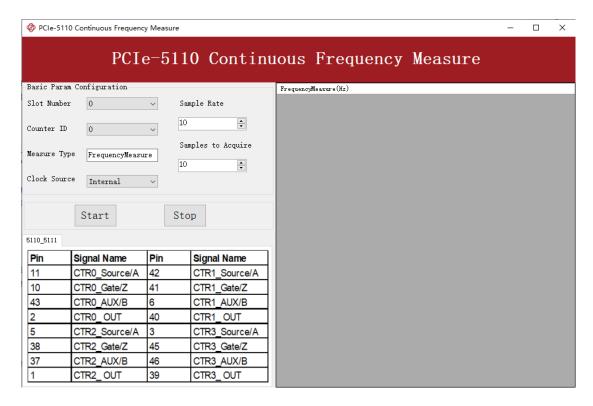

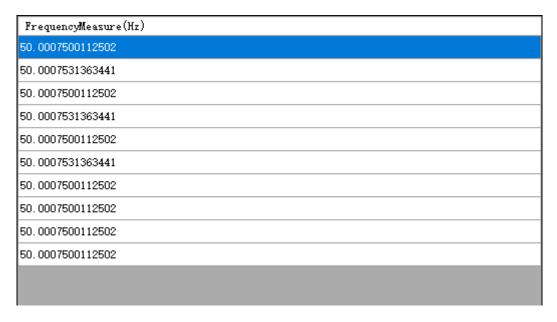

| Figure 72 Frequency    | Measure For Continuous Mode             | 73 |

| Figure 73 Frequency    | Measure Values                          | 73 |

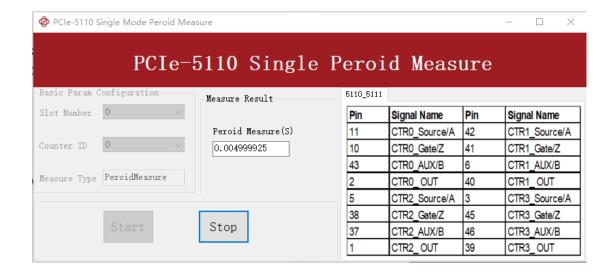

| Figure 74 Peroid Mea   | sure For Single Mode                    | 74 |

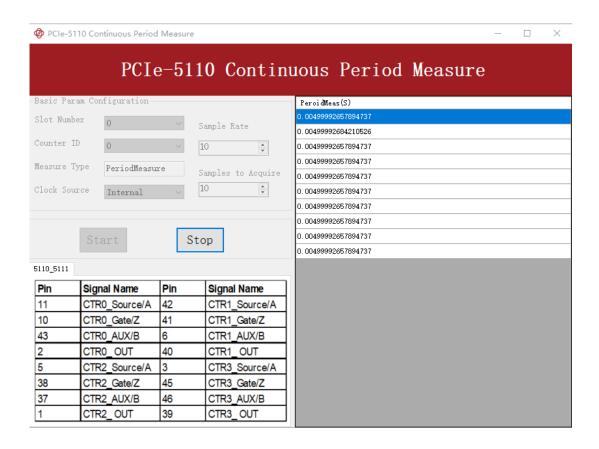

| Figure 75 Peroid Mea   | sure For Continuous Mode                | 75 |

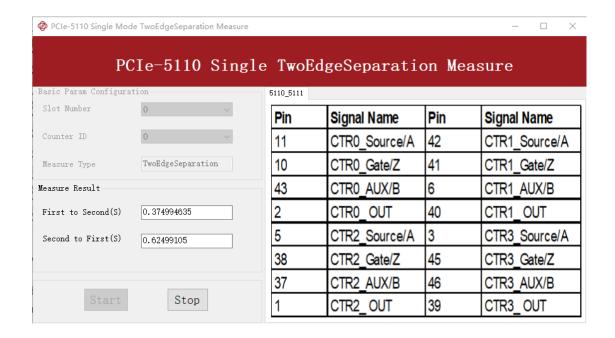

| Figure 76 Two-Edge S   | Separation in Single Mode               | 76 |

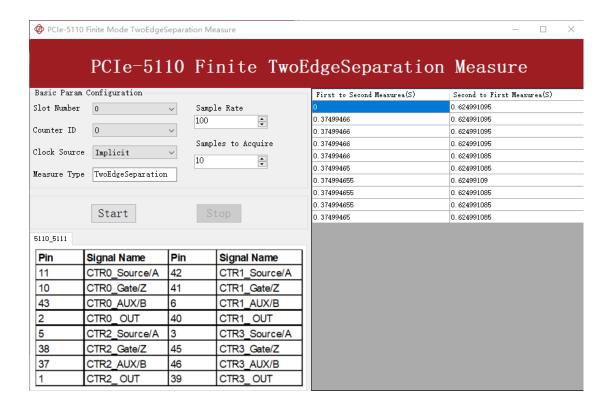

| Figure 77 Two-Edge S   | Separation with Internal Sample Clock   | 77 |

| Figure 78 Two-Edge S   | Separation with Implicit Sample Clock   | 77 |

| Figure 79 Two-EdgeS    | Separation Measure For Single Mode      | 78 |

| Figure 80 Two-EdgeS    | Separation Measure For Finite Mode      | 79 |

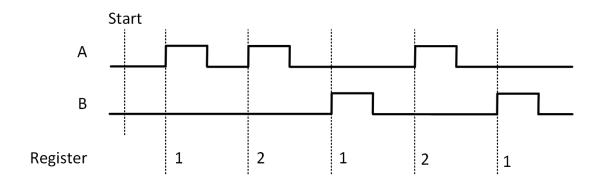

| Figure 81 Quadrature   | Encoder x1 Mode                         | 80 |

| Figure 82 Quadrature   | Encoder x2 Mode                         | 80 |

| Figure 83 Quadrature   | Encoder x4 mode                         | 81 |

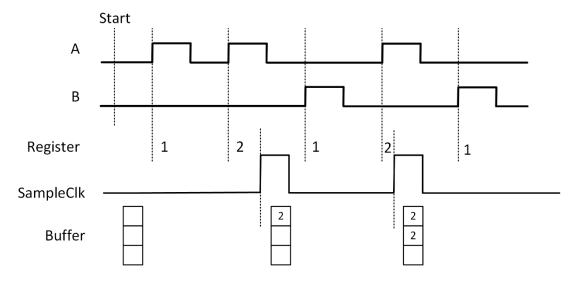

| Figure 84 Quadrature   | Encoder x1 with Sample Clock            | 82 |

| Figure 85 Quadrature   | Encoder x1 with Implicit Sample Clock   | 82 |

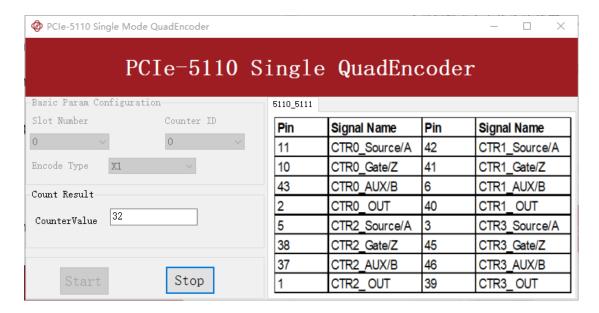

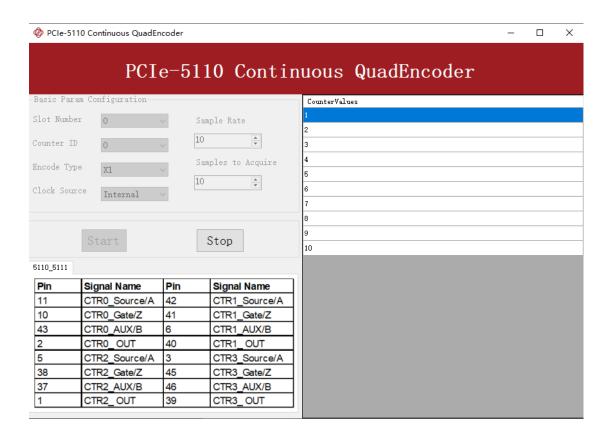

| Figure 86 QuadEncoc    | der For Single Mode                     | 83 |

| Figure 87 QuadEncoc    | der For Continuous Mode                 | 84 |

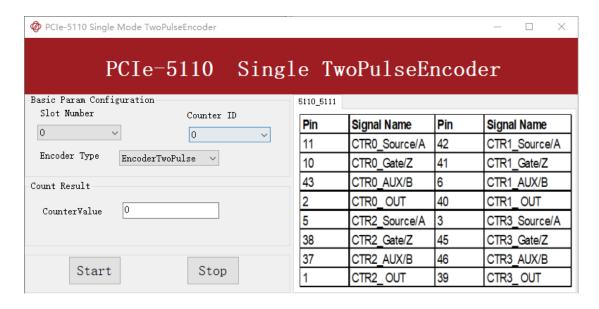

| Figure 88 Two-Pulse I  | Encoder in Single Mode                  | 85 |

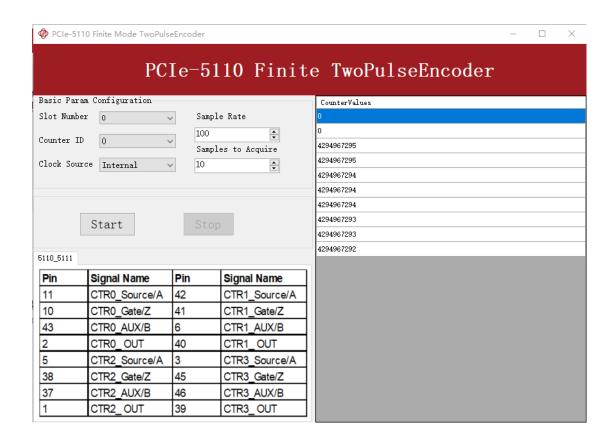

| Figure 89 Two-Pulse I  | Encoder with Internal Sample Clock      | 85 |

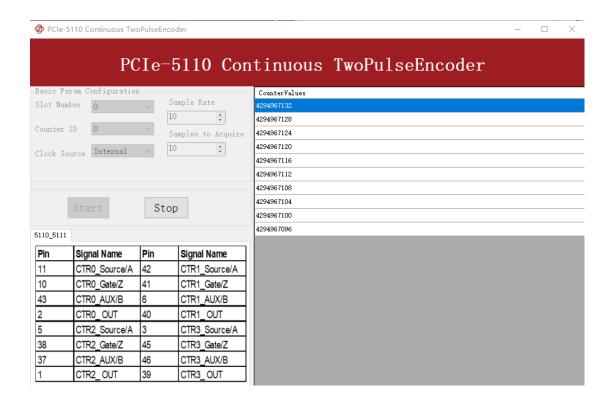

| Figure 90 Two-Pulse I  | Encoder with Implicit Sample Clock      | 86 |

| Figure 91 Two-PulseE   | Encoder For Single Mode                 | 87 |

| Figure 92 Two-PulseEncoder For Finite Mode                      | 88  |

|-----------------------------------------------------------------|-----|

| Figure 93 Two-PulseEncoder For Continuous Mode                  | 89  |

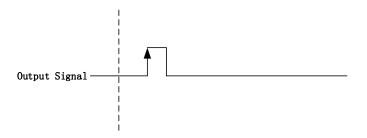

| Figure 94 Single Pulse Output                                   | 89  |

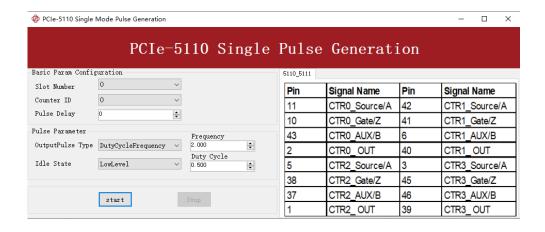

| Figure 95 Single Pulse Generation                               | 90  |

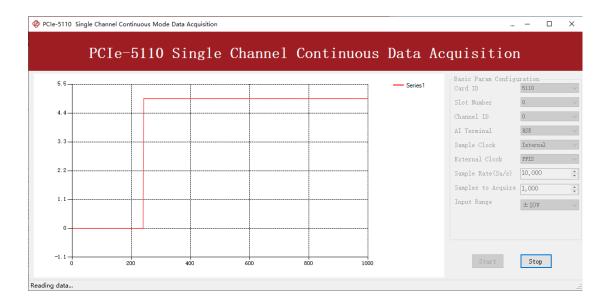

| Figure 96 Al Acquisition Single Pulse                           | 91  |

| Figure 97 Finite Pulse Output                                   | 91  |

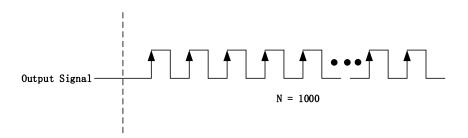

| Figure 98 Finite Pulses Generation                              | 92  |

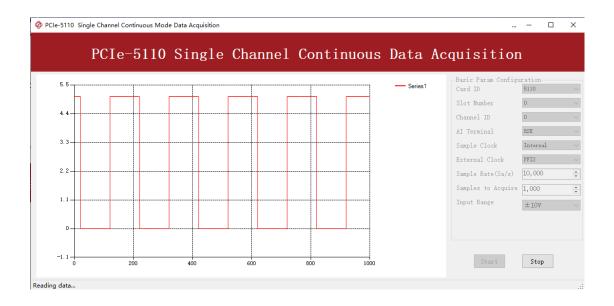

| Figure 99 Al Acquisition Finite Pulse                           | 93  |

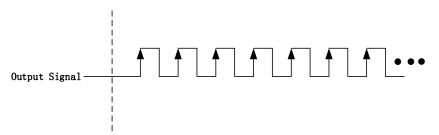

| Figure 100 Continuous Pulse Output                              | 93  |

| Figure 101 Continuous Pulse Generation                          | 94  |

| Figure 102 Al Acquisition Continuous Pulse                      | 94  |

| Figure 103 SSI Connector in PCle-5111B                          | 95  |

| Figure 104 DIP swich in PCIe-5111B                              | 96  |

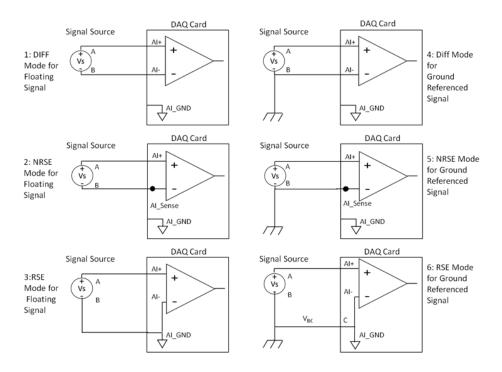

| Figure 105 Six Measurement Scenarios                            | 99  |

| Figure 106 Using Resister to Reduce Common Mode Voltage Effect. | 100 |

| Figure 107 JY-5111B Analog Input Wiring Guide                   | 101 |

# 2. Software

# 2.1. Supported Operating System

Windows 7/10, x64/x86, Linux. See additional information.

# 2.2. Programming Languages

Microsoft C#. See additional software information for other languages.

# 3. Order Information

PCIe-5111B(PN: JY8379886-01)

32-ch Al (16-Bit,500 kS/s), 4-ch AO (16-Bit,2 MS/s), 48DIO PCle Board Isolated Multifunction I/O Module

PCIe-5112B (PN: JY9786666-01)

16-ch Al (16-Bit,500 kS/s), 2-ch AO (16-Bit,2 MS/s), 24DIO PCle Board Isolated Multifunction I/O Module

Accessories:

DIN-68 (PN: JY2953885-01)

ACL-1016868-1 (PN: JY7996916-01) 1 M 68pin VHDC-SCSI twisted pair cable

ACL-1016868-2 (PN: JY7996916-02) 2 M 68pin VHDC-SCSI twisted pair cable

# 4. JYPEDIA

JYPEDIA is an excel file. It contains JYTEK product information, pricing, inventory information, drivers, software, technical support, knowledge base etc. You can register and download a JYPEDIA excel file from our web www.jytek.com. JYTEK highly recommends you use this file to obtain information from JYTEK.

# 5. Additional Hardware Information

#### 5.1. Basic DC AI Accuracy

The DAQ mode is the normal data acquisition mode commonly found in commercial DAQ hardware. The basic AI DC accuracy Table 6 of the DAQ mode provides accuracy entries when PCle-5111B operates in the single channel mode and within the indicated calibration temperature range. Please note that this accuracy is valid for every single point regardless how many sample points you acquire.

Each entry in the basic accuracy table is a pair of gain and offset coefficients. Using these gain and offset coefficients, your measurement accuracy can be calculated by following formula:

$$Accuracy = \pm (\% \ of \ Reading + \% \ of \ Range)$$

For example, at the 0.625 V range and 24 Hours column, if your measurement or reading is 0.02V, the accuracy of this measurement is:

$$\pm (0.0013\% * 0.02 + 0.0544\% * 0.625) = \pm 0.00034 \text{ V} = \pm 340 \,\mu\text{V}$$

The basic accuracy table also provides full-scale accuracy entries for a quick and convenient look-up. For example, the full-scale accuracy for the 0.625 V range and the 24-Hour calibration column is 348  $\mu$ V.

#### **5.2.** Basic AO Accuracy

The AO output accuracy of PCIe-5111B when using the analog output function can be calculated according to the corresponding parameters in the

| JY-5111B/JY-5112B AO Basic Accuracy = ±(% Output+% Range)                        |                                                               |        |           |       |     |       |         |         |       |

|----------------------------------------------------------------------------------|---------------------------------------------------------------|--------|-----------|-------|-----|-------|---------|---------|-------|

| Nominal<br>Range (V)                                                             | 24 Hour Ical $\pm 1^{\circ}$ C 90 Days Ical $\pm 5^{\circ}$ C |        | Scale     | ,     | • , |       |         |         |       |

| 10                                                                               | 0.006                                                         | +      | 0.012     | 0.015 | +   | 0.012 | 1800 uV | 2700 uV | 0.027 |

| Accuracy va                                                                      | lid to 95%                                                    | % of 1 | ull range |       |     |       |         |         |       |

| Note: The 90-day data is estimated based on multiplying the 24-hour data by 2.5. |                                                               |        |           |       |     |       |         |         |       |

Table 8 Each entry in the basic accuracy table is a pair of gain and offset coefficients. Using these gain and offset coefficients, your AO output basic accuracy is calculated by following formula:

$$Accuracy = \pm (\% \ of \ Output + \% \ of \ Range)$$

For example, at the 5V range and 24 Hours column, if your output is 2V, the accuracy of this measurement is:

$$\pm (0.0014\% * 2 + 0.0043\% * 5) = \pm 0.000243V = \pm 243 \mu V$$

The basic accuracy table also provides full-scale accuracy entries for a quick and convenient look-up. For example, the full-scale accuracy for the 5V range and the 24-Hour calibration column is 285  $\mu$ V.

# 6. Additional Software Information

## **6.1. System Requirements**

PCIe-5111B series boards can be used in a Windows or a Linux operating system.

Microsoft Windows: Windows 7 32/64 bit, Windows 10 32/64 bit.

Linux Kernel Versions: There are many Linux versions. It is not possible JYTEK can support and test our devices under all different Linux versions. JYTEK supports the following Linux versions only.

| Linux Version                                                   |

|-----------------------------------------------------------------|

| Ubuntu LTS                                                      |

| 16.04: 4.4.0-21-generic(desktop/server)                         |

| 16.04.6: 4.15.0-45-generic(desktop) 4.4.0-142-generic(server)   |

| 18.04: 4.15.0-20-generic(desktop) 4.15.0-91-generic(server)     |

| 18.04.4: 5.3.0-28-generic (desktop) 4.15.0-91-generic(server)   |

| Localized Chinese Version                                       |

| 中标麒麟桌面操作系统软件(兆芯版)V7.0(Build61): 3.10.0-862.9.1.nd7.zx.18.x86_64 |

| 中标麒麟高级服务器操作系统软件V7.0U6: 3.10.0-957.el7.x86_64                    |

Table 13 Supported Linux Versions

## **6.2. System Software**

When using the PCIe-5111B series in the Window environment, you need to install the following software from Microsoft website:

Microsoft Visual Studio Version 2015 or above,

.NET Framework version is 4.0 or above.

.NET Framework is coming with Windows 10. For Windows 7, please check .NET Framework version and upgrade to 4.0 or later version.

Given the resources limitation, JYTEK only tested PCIe-5111B be with .NET Framework 4.0 with Microsoft Visual Studio 2015. JYTEK relies on Microsoft to maintain the compatibility for the newer versions.

## **6.3.** C# Programming Language

All JYTEK default programming language is Microsoft C#. This is Microsoft recommended programming language in Microsoft Visual Studio and is particularly suitable for the test and measurement applications. C# is also a cross platform programming language.

#### 6.4. PCIe-5111B Series Hardware Driver

After installing the required application development environment as described above, you need to install the PCIe-5111B hardware driver.

JYTEK hardware driver has two parts: the shared common driver kernel software (FirmDrive) and the specific hardware driver.

Common Driver Kernel Software (FirmDrive): FirmDrive is the JYTEK's kernel software for all hardware products of JYTEK instruments. You need to install the FirmDrive software before using any other JYTEK hardware products. FirmDrive only needs to be installed once. After that, you can install the specific hardware driver.

Specific Hardware Driver: Each JYTEK hardware has a C# specific hardware driver. This driver provides rich and easy-to-use C# interfaces for users to operate various PCIe-5111B function. JYTEK has standardized the ways which JYTEK and other vendor's DAQ boards are used by providing a consistent user interface, using the methods, properties and enumerations in the object-oriented programming environment. Once you get yourself familiar with how one JYTEK DAQ card works, you should be able to know how to use all other DAQ hardware by using the same methods.

Note that this driver does not support cross-process, and if you are using more than one function, it is best to operate in one process.

## 6.5. Install the SeeSharpTools from JYTEK

To efficiently and effectively use PCIe-5111B boards, you need to install a set of free C# utilities, SeeSharpTools from JYTEK. The SeeSharpTools offers rich user interface functions you will find convenient in developing your applications. They are also

needed to run the examples come with PCIe-5111B hardware. Please register and download the latest SeeSharpTools from our website, www.jytek.com.

# 6.6. Running C# Programs in Linux

Most C# written programs in Windows can be run by MonoDevelop development system in a Linux environment. You would develop your C# applications in Windows using Microsoft Visual Studio. Once it is done, run this application in the MonoDevelop environment. This is JYTEK recommended way to run your C# programs in a Linux environment.

If you want to use your own Linux development system other than MonoDevelop, you can do it by using our Linux driver. However, JYTEK does not have the capability to support the Linux applications. JYTEK completely relies upon Microsoft to maintain the cross-platform compatibility between Windows and Linux using MonoDevelop.

# 7. Operating JY5111B

This chapter provides the operation guides for PCIe-5111B, including AI, AO, DI, DO, Timer and programmable I/O interface, etc.

JYTEK provides extensive examples, on-line help and documentation to assist you to operate the PCle-5111B board. JYTEK strongly recommends you go through these examples before writing your own application. In many cases, an example can also be a good starting point for a user application.

#### 7.1. Quick Start

After you have installed the driver software and the SeeSharpTools, you are ready to use Microsoft Visual Studio C# to operate the PCle-5111B products.

If you are already familiar with Microsoft Visual Studio C#, the quickest way to use PCle-5111B boards is to go through our extensive examples. We provide source code of our examples. In many cases, you can modify the source code and start to write your applications.

We also provide **Learn by Example** in the following sections. These examples will help you navigate and learn how to use this PCIe-5111B.

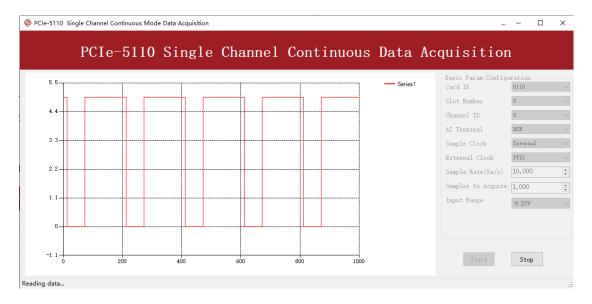

#### 7.2. Data Acquisition Methods

PCIe-5100 uses a scanning method to acquire analog data, meaning there is only one ADC chip on the device and all input channels share this ADC. In the scan acquisition mode, you need to configure AI channels and set up some parameters through PCIe-5111B driver software. The most important parameters are *Data Acquisition mode*, *Sample Rate*, *SamplesToAcquire*, *Channel Count*, *ChannelRange* and *Analog Input Terminal Type*.

Al Acquisition mode (AlMode): PCIe-5111B provides 4 acquisition modes, Continuous, Finite, Single Point, Record, which will be described in details in Section 7.2.1-7.2.4.

SampleRate: How fast data are acquired per second per channel. For example, if the sample rate is 1000Hz, you acquire two channels of data, you will have 2000 points/second.

SamplesToAcquire: This parameter behaves differently in the different AI acquisition modes. In the continuous acquisition mode, SamplesToAcuire is the buffer size used in the AI acquisition task, please see Section7.2.1; in the finite acquisition mode, it is the total number of samples to capture, please see Section7.2.2.

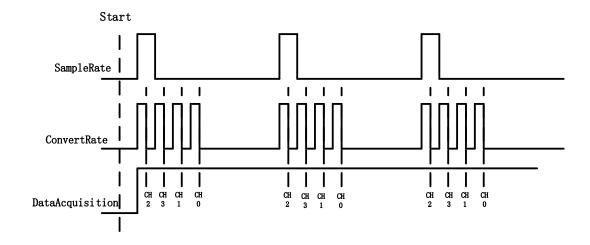

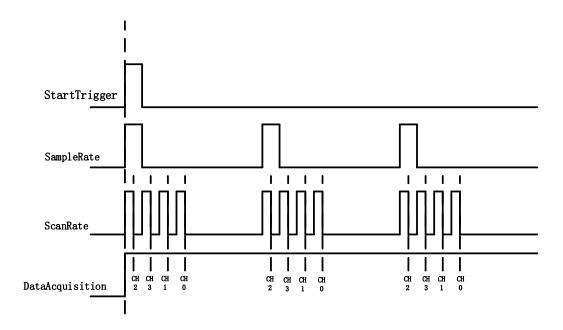

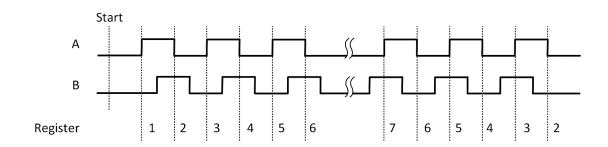

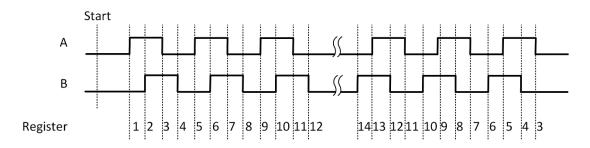

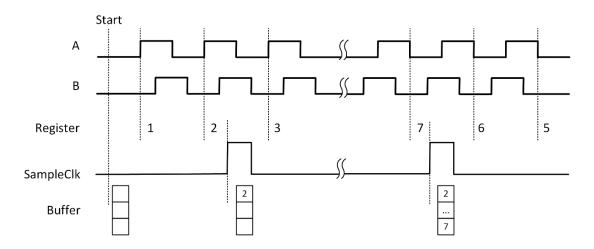

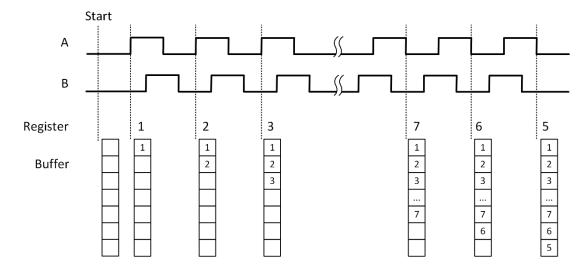

Channel Count: how many channels you want to collect data. You can set up the channels in different orders, for instance 2,3,1,0. The acquired data will be arranged in the way you specify as shown in Figure 2. In this particular case, Channel Count is 4.

Figure 2 Sample Rate and Internal AD Conversion

\* ChannelCount . User can redefine the ConvertRate in our software. If user want to redefine ConvertRate, The following conditions must be met:

Multichannel maximum sample rate (aggregate) >=ConvertRate >= SampleRate \*

ChannelCount.

User can get Multichannel maximum sample rate (aggregate) from section Appendix.

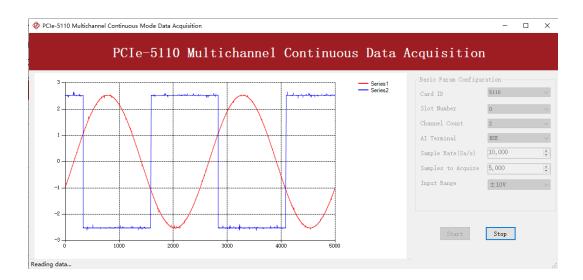

## Learn by Example 7.2

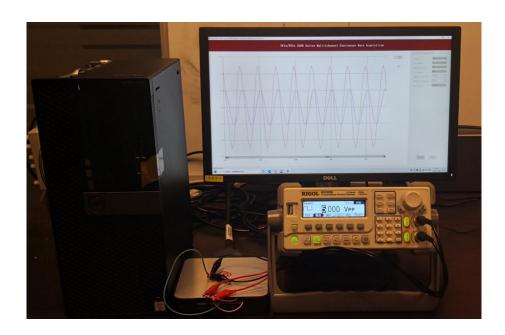

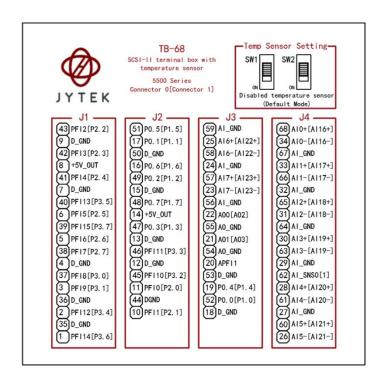

■ Connect the two signal source's positive outputs to PCIe-5111B AI Ch0 (AI0+, Pin #68) and AI Ch1 (AI1+, Pin#33), two negative terminals to the ground (AI\_GND, Pin#67) as shown in Figure 3 and Figure 4 (AI0+, AI\_GND) and (AI1+, AI\_GND) consist of two channels of RSE inputs and they share the same GND.

Figure 3 PCIe-5111B experiment

Figure 4 TB-68 Terminal Block

- Set a sinewave signal (f=4Hz, Vpp=5V) and a squarewave signal (f=4Hz, Vpp=5V).

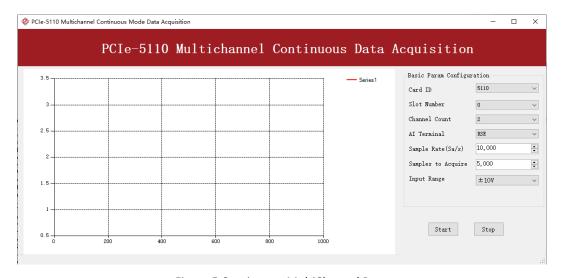

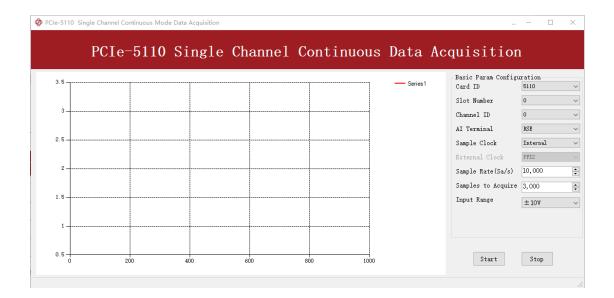

- Open Analog Input-->Winform AI Continuous MultiChannel, set the following numbers as shown. This sample program will continuously acquire data from multiple channels.

Figure 5 Continuous MultiChannel Paraments

SampleRate is set by Sample Rate

- Samples to Acquire is the samples to be acquired for each channel in one block.

The continuous mode will acquire blocks after blocks until **Stop** button is pressed.

- When start is clicked, it generates a software trigger, which starts the acquisition.

The result is shown below.

Figure 6 MultiChannel Continuous Acquisition

### 7.2.1. Continuous Acquisition

An AI acquisition task will acquire the data continuously until the task is stopped. The PCIe-5111B device will continue acquiring data and save the data in a circular buffer. You specify how many samples to read back by the user buffer's length, if your program does not read the data fast enough, the circular buffer may overflow. In this case, the driver software will throw out an error message.

*Tip*: User buffer's length 1/10<sup>th</sup> to 1/4<sup>th</sup> *SampleRate* is a good start.

#### 7.2.2. Finite Acquisition

In the Finite Acquisition mode, an AI acquisition task will capture specific total number of samples by the parameter, SamplesToAcquire.

You can use the sample program **Analog Input --> Winform AI Finite** to learn more about Finite Acquisition.

#### 7.2.3. Single Point Acquisition

In the Single Acquisition mode, it is to capture a single sample for each acquisition.

You can use sample program: **Analog Input --> Console AI Single Point** to learn more about the single point Acquisition.

#### 7.2.4. Record Acquisition

Al Task will continuously capture the data and then save them to a storage disk. During the capturing process, user can preview the captured data randomly when the capturing process is available. The mode is particularly useful for high-speed acquisition and recording applications.

## 7.3. Analog Input Terminal Type

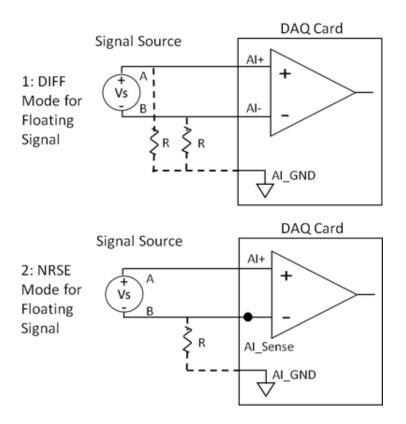

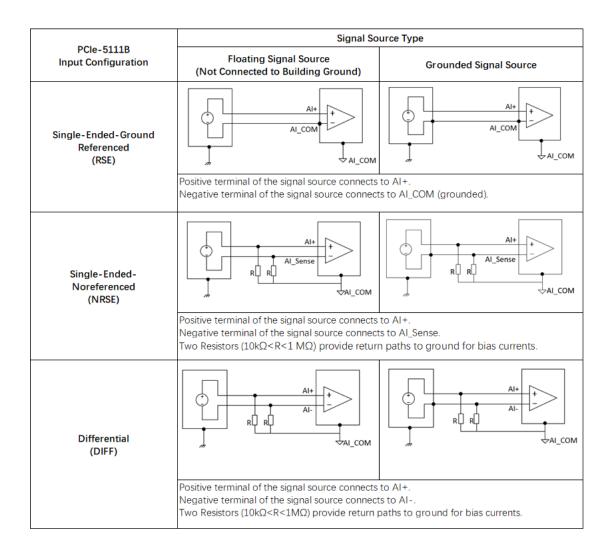

The PCIe-5111B provide 3 analog input terminal types:

- Differential (DIFF)

- Referenced Single-Ended (RSE)

- Non-Referenced Single-Ended (NRSE)

The DIFF connection is recommended for ground-referenced signal sources and it is usually better in rejecting the common-mode noise. However, to acquire one input signal, two AI channels are required to form the differential pair. The RSE and NRSE are recommended when the input signal sources are floating signals. In RSE and NRSE modes, these floating signal sources all share the same ground reference (AI\_GND). Because of it, the RSE and NRSE modes can acquire twice as many channels than the DIFF mode. Appendix has more details on these 3 modes.

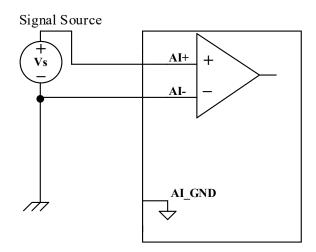

#### **7.3.1. DIFF Mode**

The DIFF mode connects signal's positive side to Al's positive input, signal's grounded negative side to Al's negative input as shown in Figure 7. The common noise appears on both positive and negative terminals of the differential amplifier;

thus it will be cancelled out. Therefore, the DIFF mode has better signal-to-noise ratio (SNR). Please see Appendix for more explanations.

Figure 7 Differential Mode for Grounding Signals

## Learn by Example 7.3.1

- Open the program Analog Input-->Winform AI Continuous MultiChannel

- Connect the two signal source's positive outputs to PCIe-5111B AI Ch0 (AI0+, Pin #68) and AI Ch1 (AI1+, Pin#33), two negative terminals to AI Ch0 negative (AI0-, Pin#34) and AI Ch1 negative (AI1-, Pin#66) as shown in Figure 3 and Figure 4. (AI0+, AI0-) and (AI1+, AI1-) consist of two pairs of DIFF inputs;

- Choose Differential in **Al Terminal**;

- Set other numbers as shown and click start.

Figure 8 Choose Differential in AI Terminal

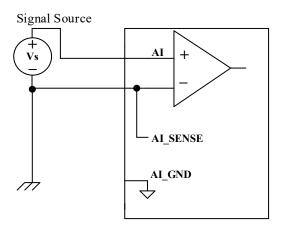

#### 7.3.2. RSE Mode

In the RSE mode, all input signals' negative sides are connected to the AI ground of Instrumentation Amplifier, as shown in Figure 9. This mode works for measurements from floating sources. The RSE mode is suitable when these two conditions exist:

- The input signals are floating, meaning they are not connected to the ground

- When the common mode noise is low, meaning a clean environment.

The RSE mode offers twice as many measurement channels as the DIFF mode. Please see Appendix for more explanations.

Figure 9 RSE Mode for Floating Signals

#### **7.3.3. NRSE Mode**

The NRSE mode is recommended for the measurement of ground-referenced signals, as shown in Figure 10. NRSE is also called the pseudo differential mode, because it looks very similar to a DIFF connection. In this mode, the PCIe-5111B device offers a special reference point, AI SENSE. Instead of connecting two grounds directly, signal's ground and PXI device's ground, the input signals' ground is connected to AI SENSE to avoid the ground loop bias. The PCIe-5111B is also designed to better reject the common mode noise than the RSE mode. Therefore, the NRSE model still offers twice many channels as the DIFF mode. Please see Appendix for more explanations.

Figure 10 NRSE Mode for Grounding Signals

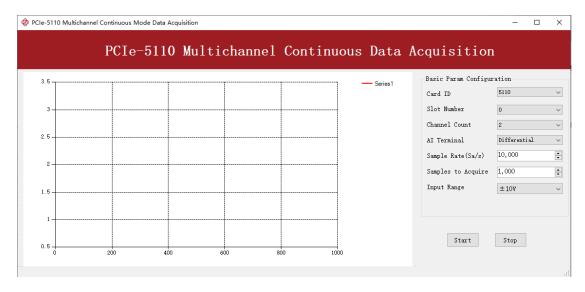

### Learn by Example 7.3.3

- Open the program Analog Input-->Winform AI Continuous MultiChannel.

- This Example needs two TB-68 terminal blocks, Connector0 and Connector1 and two cables, which are connected to PCIe-5111B. Connect the two signal source's positive outputs to PCIe-5111B AI Ch0 (AI0+, Pin #68) and AI Ch1 (AI1+, Pin#33), two negative terminals to AI\_SENSE 0 (Pin#62) of the first TB-68 and AI\_SENSE 1 (Pin#62) of the second TB-68 as shown in Figure 3 and Figure 4. (AI0+, AI\_SENSE 0) and (AI1+, AI\_SENSE 1) consist of two channels of NRSE inputs.

- Choose the NRSE in Al Terminal

- Set other numbers as shown and click start.

Figure 11 Choose NRSE In Al Terminal

# 7.4. Trigger Source

There are 4 trigger types: Immediate trigger, Software trigger, Analog trigger, and Digital trigger. The trigger type is a property and set by driver software.

## 7.4.1. Immediate trigger

This trigger mode does not require configuration and is triggered immediately when an operation starts. The operation can be AI, AO, DI, DO, CI, CO etc.

## Learn by Example 7.4.1

■ Use the same program and connection as in **Learn by Example7.2.**

Figure 12 Immediate trigger Paraments

➤ With Immediate trigger you can click **Start** to generate the task instead of sending a trigger signal.

### 7.4.2. Software Trigger

A software trigger must be configured by the driver software. The trigger starts when a trigger software routine is called.

#### Learn by Example 7.4.2

- Connect the signal source's positive terminal to PCIe-5111B AI Ch0 (AI0+, Pin#68), the negative terminal to the ground (AI\_GND, Pin#67) as shown in Figure 3 and Figure 4. (AI0+, AI GND) consists of a RSE input.

- Set a sinewave signal (f=4Hz, Vpp=5V).

- Open **Analog Input-->Winform AI Continuous Soft Trigger**, set the following numbers as shown.

- Click **Start** to run the task.

Figure 13 Software trigger Paraments

- > Data will not be acquired until there is a positive signal from *Software*Trigger when **Send Soft Trigger** is clicked.

- After sending the trigger signal, the result will be like this:

Figure 14 Software trigger Acquisition

## 7.4.3. External Analog Trigger

You can assign one of measurement channels as the analog trigger source. PCle-5111B provides three analog trigger modes:

- Edge comparator,

- Hysteresis comparator,

- Window comparator.

Analog trigger threshold range can be arbitrarily selected in the effective range of the selected channel. When setting the threshold, please pay attention to the physical unit currently in use.

#### **Edge comparator**

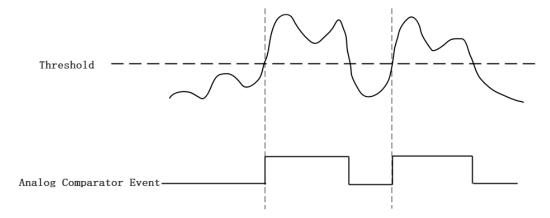

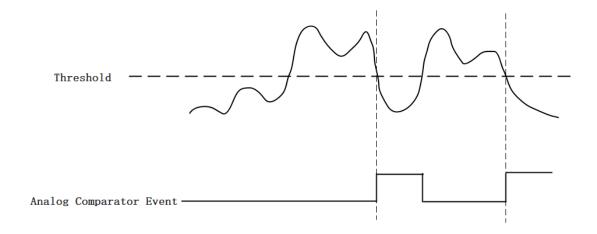

In the Edge comparator, there are two trigger conditions: *Rising Slope Trigger* and *Falling Slope Trigger*.

Rising Slope Trigger: The Edge comparator output is high when the signal goes above the threshold; the output is low when the signal goes below the threshold as shown in Figure 15.

Falling Slope Trigger: The Edge comparator output is high when the signal goes below the threshold; the output is low when the signal goes above the threshold as shown in Figure 16.

Figure 15 Rising Slope Trigger

Figure 16 Falling Slope Trigger

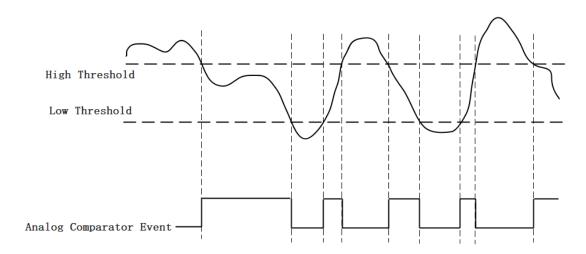

#### **Hysteresis Comparator**

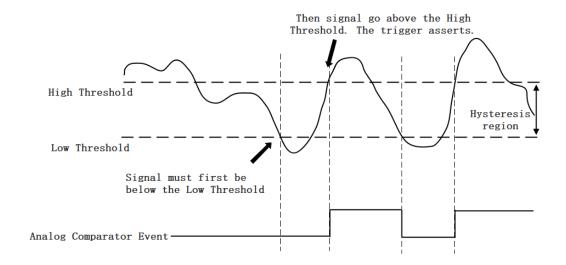

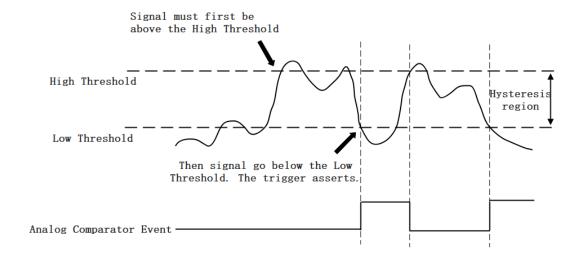

The hysteresis comparator is designed for preventing spurious triggering. You can set hysteresis region by setting high threshold and low threshold. There are two trigger conditions: *Hysteresis with Rising Slope Trigger* and *Hysteresis with Falling Slope Trigger*.

Hysteresis with Rising Slope Trigger: The Hysteresis comparator output is high when the signal must first be below the low threshold, then goes above the high threshold. The output will change to low when the signal goes below the low threshold as shown in Figure 17.

Hysteresis with Falling Slope Trigger: The Hysteresis comparator output is high when the signal must first be above the high threshold, then goes below the low threshold. The output will change to low when the signal goes above the high threshold as shown in Figure 18.

Figure 17 Hysteresis with Rising Slope Trigger

Figure 18 Hysteresis with Falling Slope Trigger

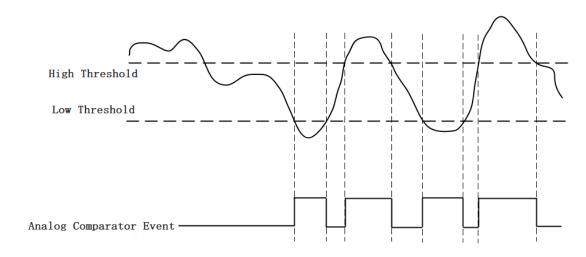

#### Window comparator

The window comparator is designed to acquire signal from interesting window by setting High Threshold and Low Threshold. There are two trigger conditions: *Entering Window Trigger* and *Leaving Window Trigger*.

Entering Window Trigger: The window comparator output is high when the signal enters the window defined by the Low Threshold and High Threshold. The output will change to low when the signal leaves the window as shown in Figure 19.

Leaving Window Trigger: The window comparator output is high when the signal leaves the window defined by the Low Threshold and High Threshold. The output will change to low when the signal enters the window as shown in Figure 20 Leaving Window Trigger.

Figure 19 Entering Window Trigger

Figure 20 Leaving Window Trigger

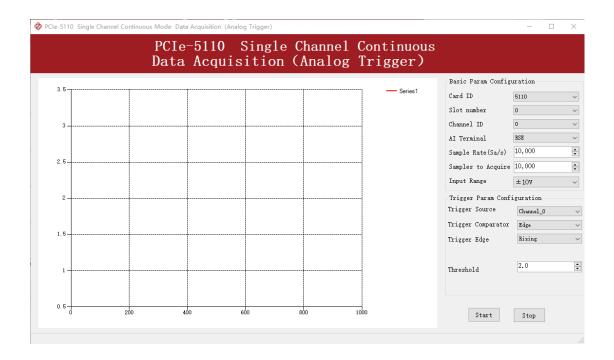

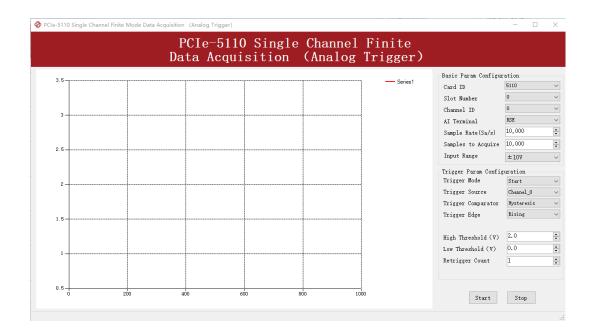

#### Learn by Example 7.4.3

- Connect the signal source's positive terminal to PCIe-5111B AI Ch0 (AI0+, Pin#68), the negative terminal to the ground (AI\_GND, Pin#67) as shown in Figure 3 and Figure 4. (AI0+, AI\_GND) consists of a RSE input.

- Set a sinewave signal (f=4Hz, Vpp=5V).

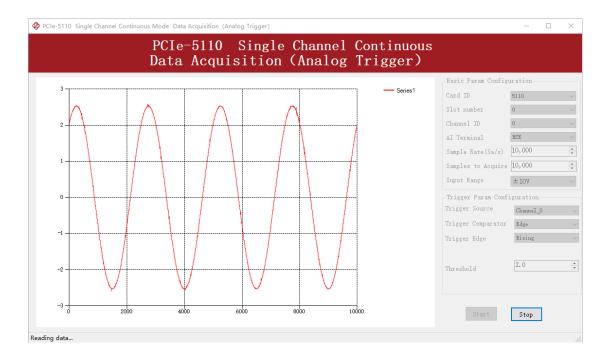

■ Open Analog Input-->Winform AI Continuous Analog Trigger, set the following numbers as shown.

Figure 21 Analog Trigger Paraments

- ➤ Modes of the *Analog Trigger* are set by **Trigger Comparator.** Set it to **Edge**.

- > The edge of *EdgeComparator* set by **Trigger Edge**. (**Rising** and **Falling**)

- Trigger source can be any channel of PCIe-5111B analog input. Set it to Channel 0.

- According to the rules of **Rising** mentioned above, the signal acquisition will not start until it raises to 2.0 V, which is set by **Threshold** above.

- Click Start, a message will appear in the lower left corner:

Figure 22 Waiting For Trigger

This indicates the data acquisition will start only after a triggering event. In this example a trigger signal will occur when the *hysteresis comparator* meets the condition explained in **7.4.3**.

#### ■ The result is shown below:

Figure 23 Analog Trigger Acquisition

The signal starts at 2.0V, which matches the Edge mode set before.

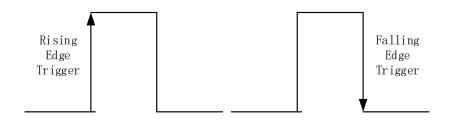

## 7.4.4. External Digital Trigger

PCIe-5100 supports different external digital trigger sources from PXI Trigger bus (PXI\_TRIG<0..7>), PXI\_STAR and connectors of front panel (PFI). The high pulse width of digital trigger signal must be longer than 20 ns for effective trigger. The module will monitor the signal on digital trigger source and wait for the rising edge or falling edge of digital signal which depending on the set trigger condition, then cause the module to acquire the data as shown in Figure 24

Figure 24 External Digital Trigger

## Learn by Example 7.4.4

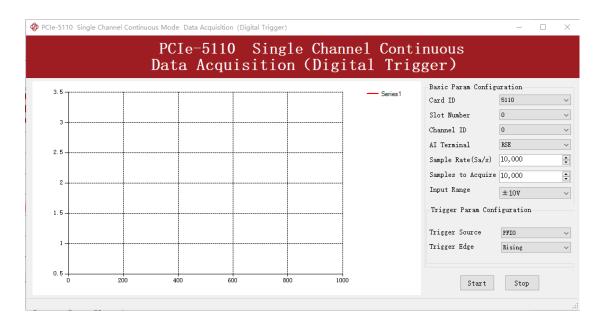

- Connect the signal source two positive terminals to PCle-5111B AI Ch0, (AIO+, Pin #68) and digital trigger source (PFI 0, Pin#11), two negative terminals to the ground of analog input (AI\_GND, Pin#67) and the ground of digital input/output (DGND, Pin#44) as shown in Figure 3 and Figure 4 (AIO+, AI\_GND) consists of a RSE input. (PFI0, DGND) provides the trigger signal.

- Set a sinewave signal (f=4Hz, Vpp=5V) and a squarewave signal (f=4Hz, Vpp=5V).

- Open Analog Input-->Winform Al Continuous Digital Trigger, set the following numbers as shown.

Figure 25 Digital Trigger Paraments

Trigger Source must match the pin on 5110.

- > There are two **Trigger Edge**: **Rising** and **Falling**.

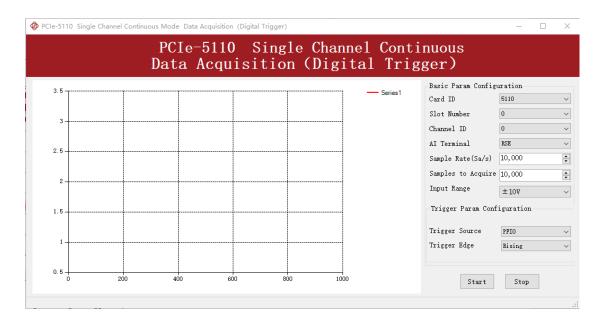

- Click Start and the result shows below:

Figure 26 Digital Trigger Acquisition

Since the squarewave is used for the digital trigger source, when a rising edge of the squarewave occurs, the digital trigger will be activated, and the data acquisition will start.

# 7.5. Trigger Mode

The PCle-5111B's analog inputs support several trigger modes: start trigger, reference trigger, and re-trigger.

#### 7.5.1. Start Trigger

In this mode, data acquisition begins immediately after the trigger. This trigger mode is suitable for continuous acquisition and finite acquisition. As shown in Figure 27.

Figure 27 Start Trigger

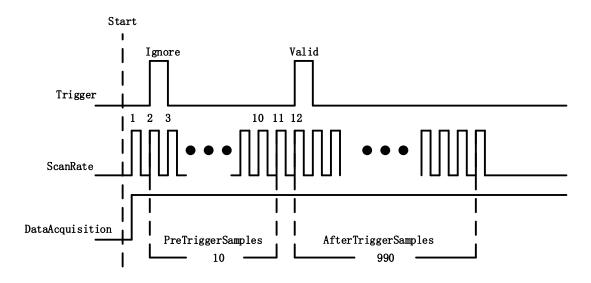

#### 7.5.2. Reference Trigger

This trigger mode is suitable for finite acquisition. In this mode, user can set the number of pre-trigger samples. The default number of pre-trigger points is 0. First you need to start the data acquisition. When the reference trigger condition is met, the routine will return the acquired data points. If when the points less than the pre-trigger samples, the trigger signal be ignored. An example is show below.

# Example

Total samples: 1000;

Channel Count: 1

Pre-trigger samples: 10;

After triggering, it returns total 1000 samples, 10 being pre-triggered, 990

after triggering

The principle is shown in Figure 28.

Figure 28 Reference Trigger

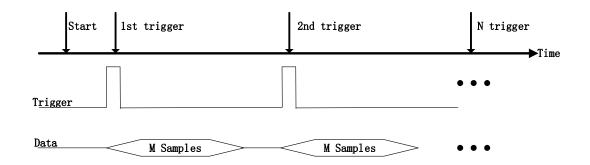

## 7.5.3. ReTrigger

PCIe-5111B supports retrigger mode. In the retrigger mode, you can set the number of retrigger and the length of each acquisition. Assuming that the number of re triggers is n and the length of each trigger acquisition is m, the length of all acquisition data is n \* m \* channelcount. Show in Figure 29.

When the number of retrigger is - 1, it is infinite.

Figure 29 ReTrigger

#### **Learn by Example 7.5**

Connect the signal source's positive terminal to PCIe-5111B AI Ch0 (AI0+, Pin#68), the negative terminal to the ground (AI\_GND, Pin#67) as shown in Figure 3 and Figure 4. (AI0+, AI\_GND) consists of an RSE input.

- Set a sinewave signal (f=4Hz, Vpp=5V).

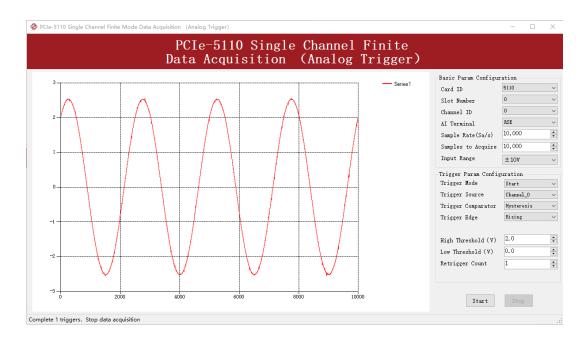

- Open Analog Input-->Winform AI Finite Analog Trigger, set the following numbers as shown.

Figure 30 Retrigger Paraments

- You can use three different kinds of triggers in this program as mentioned in 7.5.

Start Trigger and Reference Trigger can be set by Trigger Mode. For ReTrigger can be used by changing the numbers in Retrigger Count.

- PretriggerSamples is set by Pretrigger Samples.

- Now the trigger is a **Start Trigger**. Click **Start** to begin the data acquisition, the result is shown below:

Figure 31 Retrigger In Start Trigger Mode

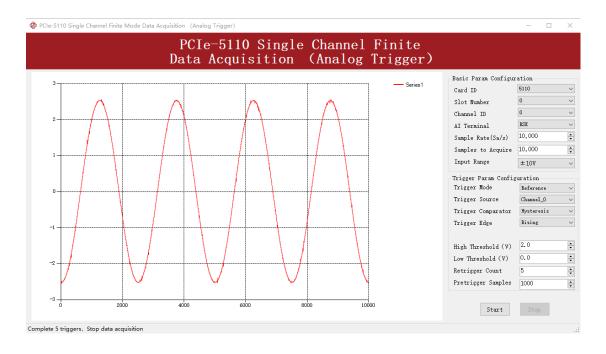

■ Now change the **Trigger Mode** to **Reference** mode with **Pretrigger Samples**1000. A different result shows below:

Figure 32 Retrigger In Reference Trigger Mode

You can see the horizontal movement between two signals due to the change of Trigger Mode.

Now change the mode of trigger to *Retrigger* through giving **Retrigger Count** a number other than 0 and click **Start**. A message will appear in the lower left corner: "Complete the  $n^{th}$  trigger".

# Complete the 2th trigger

Figure 33 Complete Retrigger Count

It shows the acquisition process through every trigger signal.

# 7.6. AO Operations

The PCIe-5111B AO provides 16-bit simultaneous outputs. The analog output has three modes of operation: Finite, ContinuousWrapping, and ContinuousNoWrapping.

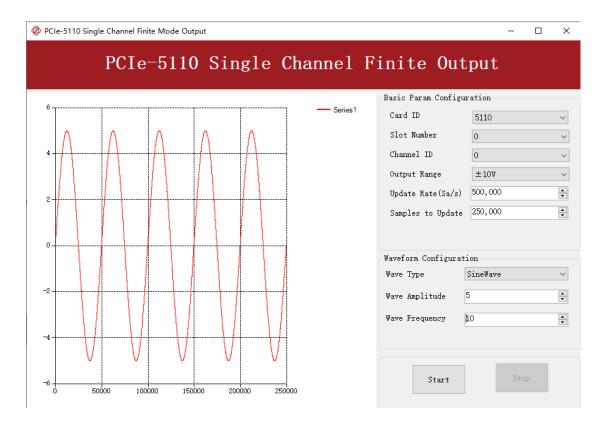

#### 7.6.1. Finite Output

The finite output requires the user to write a piece of data. After starting the AO, it starts to output the written data until the output is completed.

#### Learn by Example 7.6.1

- Connect PCIe-5111B AO Ch0 (AO0, Pin #22) to AI Ch0 (AI0+, Pin#68), Ground of AO0 (AO\_GND, Pin#55) to Ground of AI0 (AI\_GND, Pin#67). (AI0+, AI\_GND) consists of a RSE input; (AO0, AO\_GND) consists of an output.

- PCIe-5111B sends an analog signal through (AOO, AO\_GND) and reads back the signal from (AIO+, AI GND).

- Open Analog Input-->Winform AI Continuous, set the following numbers as shown.

Figure 34 AI Continuous Paraments

- Click **Start** to start the data acquisition.

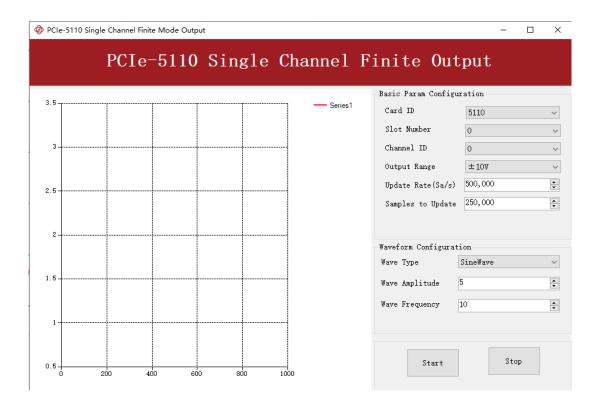

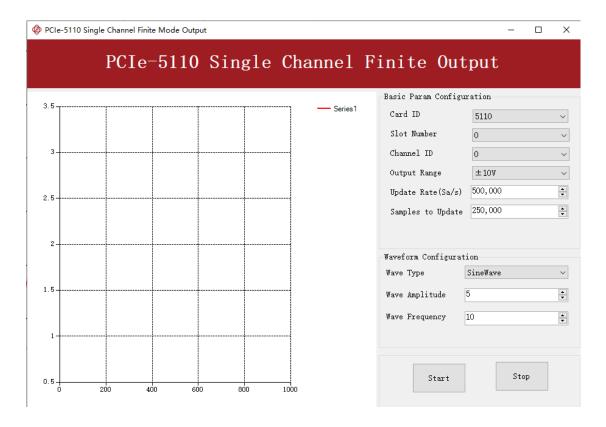

- Open Analog Output-->Winform AO Finite, set the following numbers as shown:

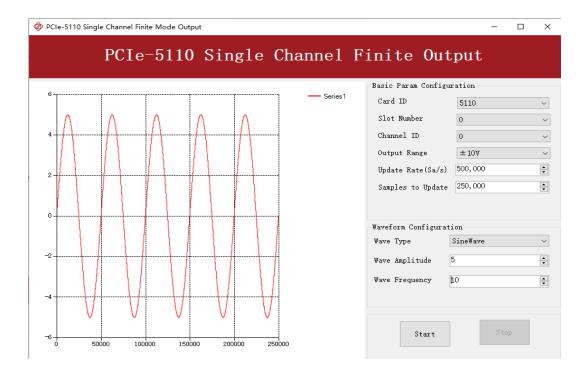

Figure 35 AO Finite Output Paraments

■ Click **Start** to generate a **SineWave**. The generated signal is shown below:

Figure 36 AO Finite Signal

■ And the received signal is shown below.

Figure 37 AI Acquisition Signal

➤ The analog signal is successfully generated and received by PCIe-5111B.

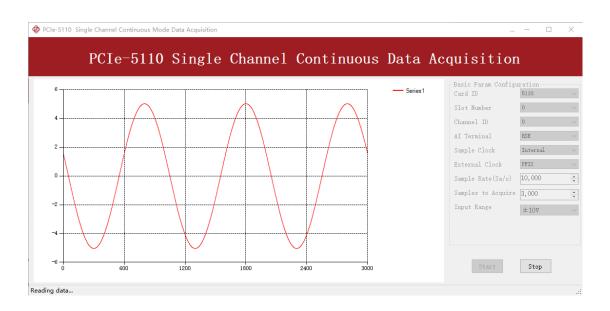

## 7.6.2. Continuous NoWrappping Output

The continuous acyclic output needs to write a piece of data before starting the AO. After the AO starts, user needs to continuously write new data to ensure the continuous output of the AO.

# Learn by Example 7.6.2

- Connect PCIe-5111B AO Ch0 (AO0, Pin #22) to AI Ch0 (AI0+, Pin#68), Ground of AO0 (AO\_GND, Pin#55) to Ground of AI0 (AI\_GND, Pin#67). (AI0+, AI\_GND) consists of a RSE input; (AO0, AO\_GND) consists of an output.

- PCIe-5111B sends an analog signal through (AOO, AO\_GND) and reads back the signal from (AIO+, AI\_GND).

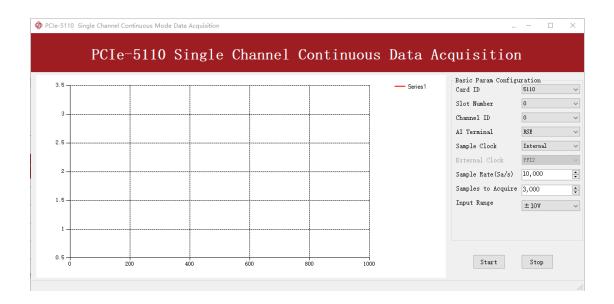

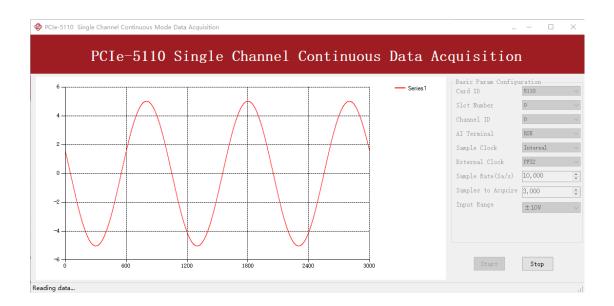

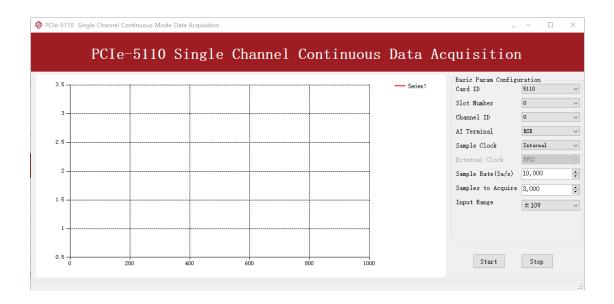

- Open Analog Input-->Winform AI Continuous, set the following numbers as shown.

Figure 38 AI Continuous Paraments

- Click **Start** to start the data acquisition.

- Open Analog Output-->Winform AO Continuous NoWrapping, set the following numbers as shown:

Figure 39 AO ContinuousNoWrapping Output Paraments

- In no wrapping analog output you can change the parameter of the signal whenever you want in **Waveform Configuration** when generating the wave.

After the configuration you should click **Update** to apply the changes.

- Click **Start** to generate a sine wave first. The result is shown below.

Figure 40 AO ContinuousNoWrapping Signal

■ And the received signal is shown below.

Figure 41 AI Acquisition AO Sin Signal

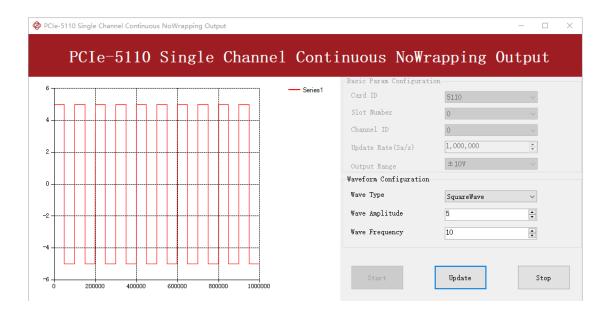

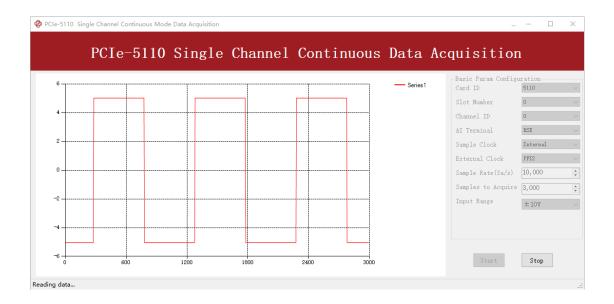

■ Now change the **Wave Type** to **SquareWave** and click **Update** to generate it. The result is shown below.

Figure 42 Update AO Square Signal

And the received signal is shown below.

Figure 43 AI Acquisition AO Square Signal

➤ The analog signal is successfully generated and received by PCIe-5111B.

## 7.6.3. Continuous Wrapping Output

The continuous loop output first writes a piece of data before starting the AO. After the AO starts, the board will repeatedly output this data until user sends a stop command.

#### Learn by Example 7.6.3

- Connect PCIe-5111B AO Ch0 (AO0, Pin #22) to AI Ch0 (AI0+, Pin#68), Ground of AO0 (AO\_GND, Pin#55) to Ground of AI0 (AI\_GND, Pin#67). (AI0+, AI\_GND) consists of a RSE input; (AO0, AO GND) consists of an output.

- PCIe-5111B sends an analog signal through (AOO, AO\_GND) and reads back the signal from (AIO+, AI\_GND).

- Open Analog Input-->Winform AI Continuous, set the following numbers as shown.

Figure 44 AI Continuous Paraments

- Click Start to start the data acquisition.

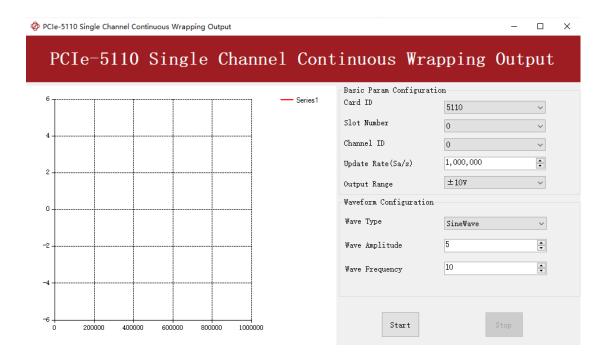

- Open Analog Output-->Winform AO Continuous Wrapping, set the numbers as shown.

Figure 45 AO Continuous Wrapping Paraments

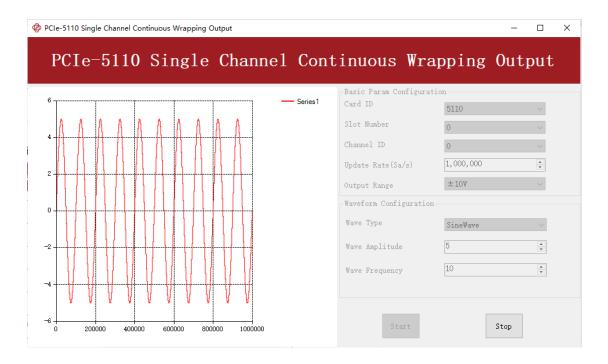

Click Start to generate the signal. The result is shown below.

Figure 46 AO Continuous Wrapping Signal

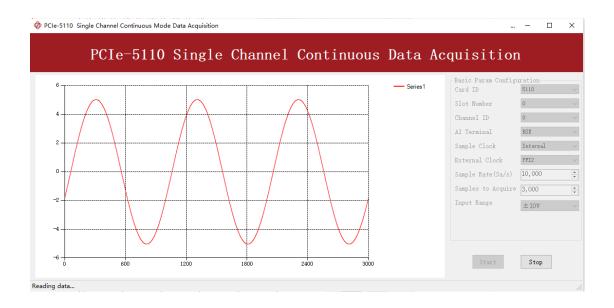

And the received signal is shown below.

Figure 47 AI Acquisition AO Signal

The analog signal is successfully generated and received by PCIe-5111B.

## 7.7. Digital I/O Operations

The PCIe-5111B provides powerful programmable digital I/O functions.

## 7.7.1. Static DI/DO

Programmable I/O supports static TTL, 6 ports (0,1,2,3,4,5) which are in total 48 digital I/O channels. User can acess these I / O information through software polling.

## Learn by Example 7.7.1

- In this example PCle-5111B outputs a digital signal by its DO function and reads it back by its DI function.

- Connect Connector1 of PCle-5111B to the TB-68 terminal block according to Figure 4.

- Connect Port 1/Line 0~7 (P1.0~P1.7) to Port 2/Line 0~7 (P2.1~2.7).PCle-5111B sends a digital signal through Port 1 and reads the signal back from Port 2.

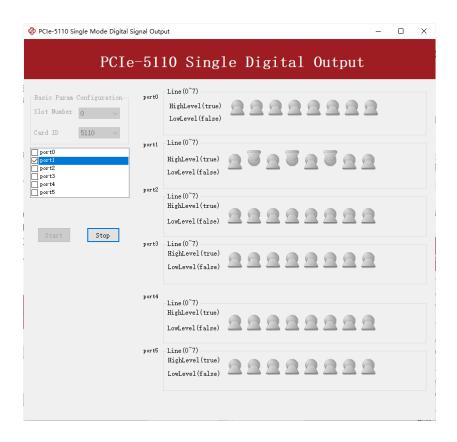

- Open the first program **Digital Output-->Winform DO SinglePoint.**

- Select **port 1** for **Digital Output**, Set Line 1,3,5 in High-Level positions, make sure all other lines are in Low-Level positions. Click **Start** to generate the High-Levels as shown.

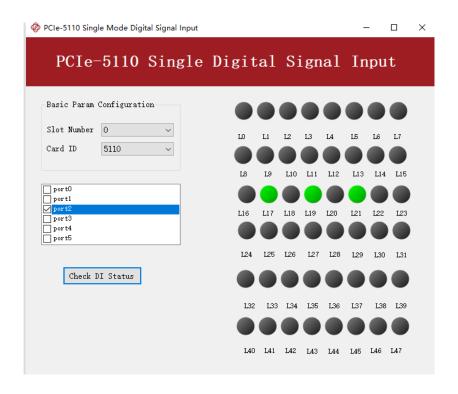

- Open the second program **Digital Input-->Winform DI SinglePoint**.

- Select port 2 for Digital Input as shown, and click Check DI Status. The result is shown below.

Figure 48 Single Digital Output

Figure 49 Single Digital Input

The result matches the high and low levels set before.

#### 7.7.2. Dynamic DI/DO

The PCIe-5111B supports both dynamic DI/DO operation with a maximum sample rate (update rate) of up to 10MHz. User can acquire or output digital waveforms in this way.

#### Learn by Example 7.7.2

- In this example PCIe-5111B outputs a squarewave by its DO function and reads it back by its DI function.

- Connect Connector1 of PCle-5111B

- Connect PCle-5111B/5111B Port 1/Line 0 (P1.0,pin#52) to Port 2/Line 0(P2.0,pin #11)

- PCIe-5111B sends digital signals through Port 1/Port 0 and reads them back from Port 2/Port 1

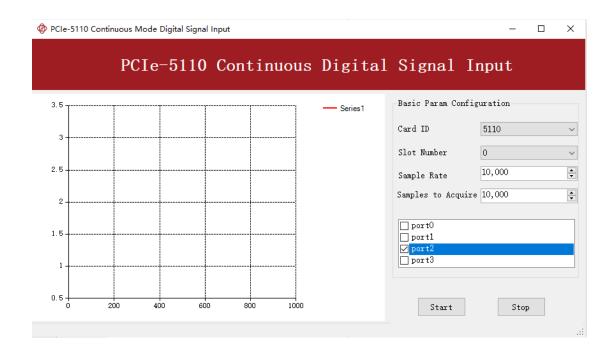

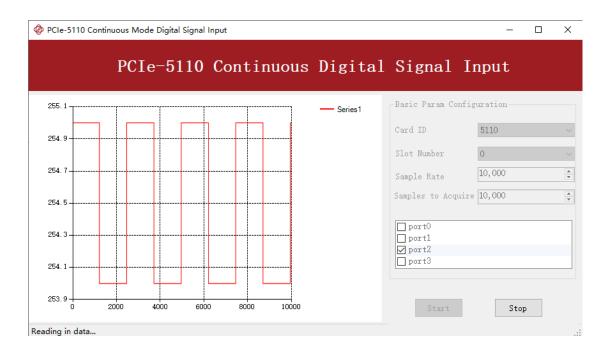

- Open Digital Input-->Winform DI Continuous and set the numbers as shown.

Select port 2(PCIe-5110/5111B) or port 1(PCIe-5110/5111B).

Figure 50 DI Continuous Paraments

- Click **Start** to begin the data acquisition.

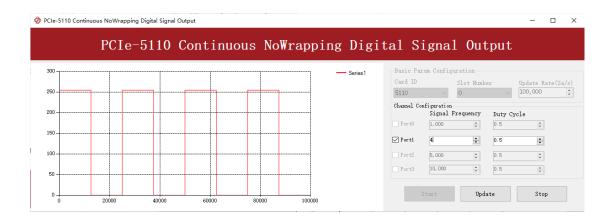

- Open Digital Output--> Winform DO Continuous NoWrapping and set the numbers as shown.

- Click **Start** to generate the signal. The result is shown below.

Figure 51 DO ContinuousNoWrapping Output

■ In program Winform DI Continuous, you can see the acquired signal. Select port 1(PCIe-5110/5111B) or port 0(PCIe-5110/5111B).

Figure 52 DI Continuous Acquisition

➤ The digital signal is successfully generated and acquired by PCle-5111B.

# 7.8. Counter Input Operations

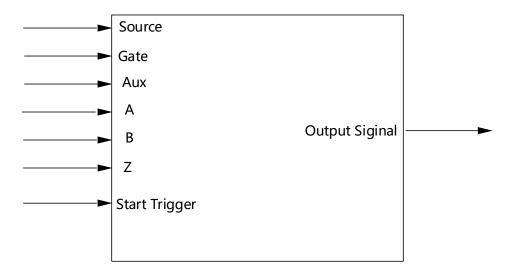

The PCIe-5111B has four or two identical 32 bits timers/counters.

Figure 53 Counter Terminal

Each counter has seven input terminals and one output terminal, and these terminals have different functions in different counter input application types, including:

- Edge Counting

- Pulse Measurement

- Frequency Measurement

- Period Measurement

- Two-Edge Separation

- Quadrature Encoder (X1, X2, X4)

- Two-Pulse Encoder

For buffered acquisition, each counter has a separate DDR storage space and requires a sample clock.

For each counter input application type, the measured signal needs to be connected to different terminals, as shown in the following table.

| Measured Signal                 | Terminal |

|---------------------------------|----------|

| Edge Counting                   | Source   |

| Pulse Measurement               | Gate     |

| Frequency Measurement           | Gate     |

| Period Measurement              | Gate     |

| Two-Edge Separation             | Gate、Aux |

| Quadrature Encoder (X1, X2, X4) | A、B、Z    |

| Two-Pulse Encoder               | A、B      |

Figure 54 Counter Signal Wiring Instruction

## 7.8.1. Edge Counting

The counter counts the number of active edges of input signal.

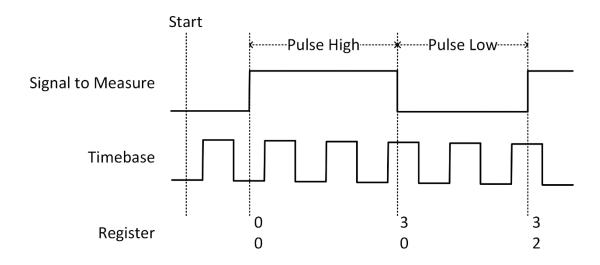

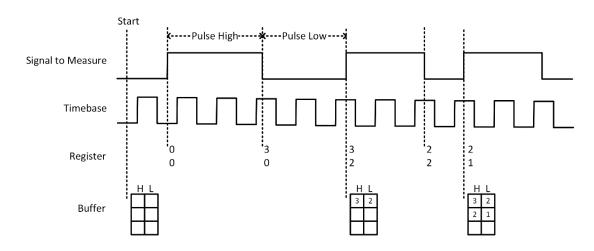

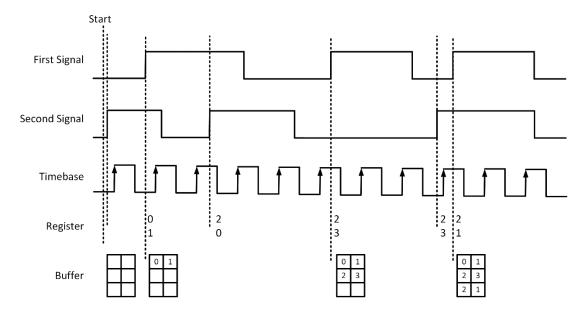

## **Timing**

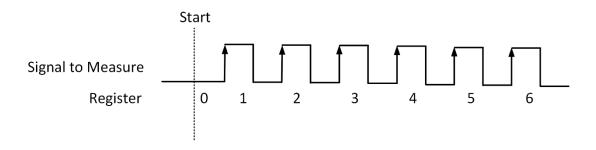

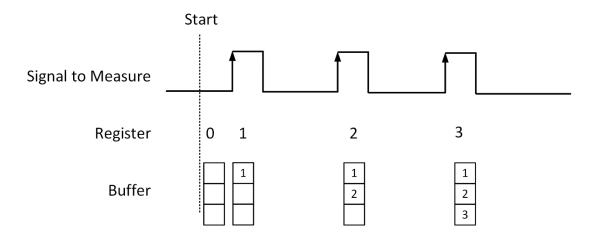

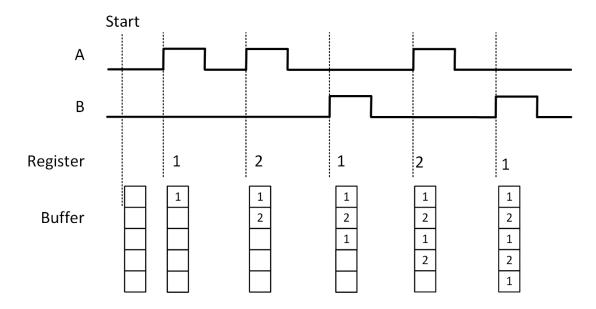

#### 1) Single Mode

The count value is written to the register on each rising edge or falling edge of the signal to measure as shown in Figure 55.

Figure 55 Simple Edge Counting in Single Mode

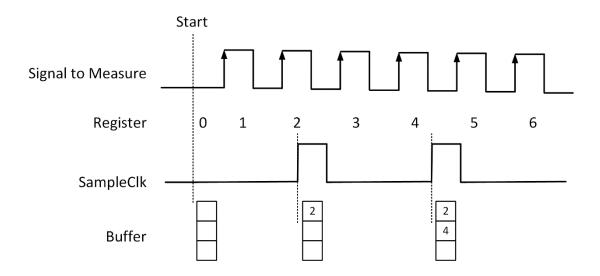

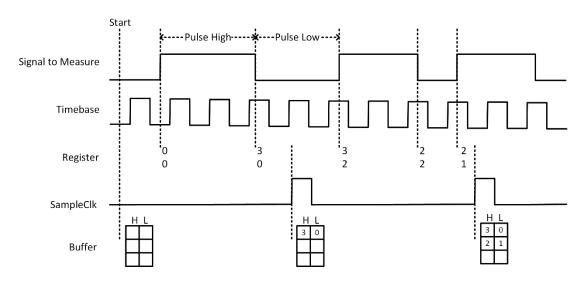

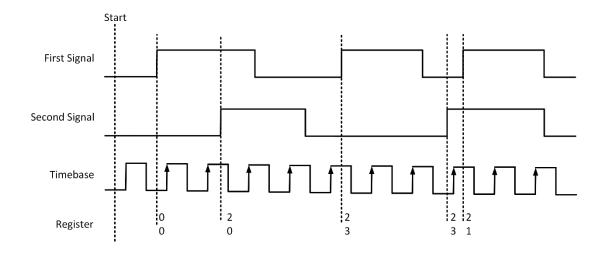

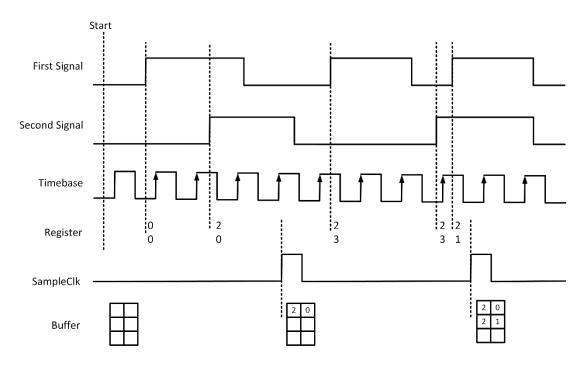

## 2) Finite/Continuous Mode with Internal Sample Clock

The count value is stored into the buffer on each rising edge or falling edge of the sample clock as shown in Figure 56.

Figure 56 Buffered Edge Counting with Internal Sample Clock

## 3) Finite/Continuous Mode with Implicit Sample Clock

The count value is stored into the buffer on each rising edge or falling edge of the signal to measure as shown in Figure 57.

Figure 57 Simple Edge Counting with Implicit SampleClk

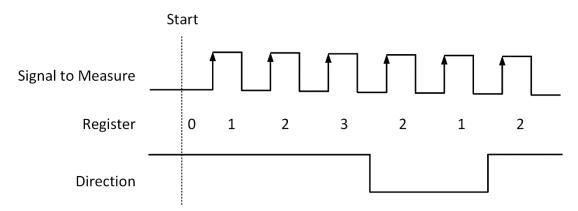

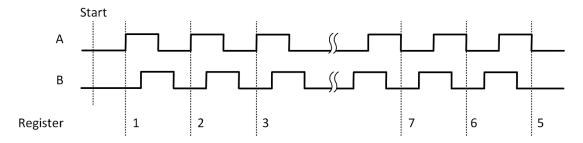

## **Counting Direction**

User can control the counting direction through software configuration or by an input signal with Gate terminal. When using an input signal to control the counting direction, the counter counts up when the signal is high and counts down when the signal is low as shown in Figure 58.

Figure 58 Count Direction

# Learn by Examples 7.8.1